Universal memory: SRAM, DRAM and flash memory in one bottle

Nowadays, there is more than one type of memory, each of which is used for a particular task. They cope with their tasks quite well, but there are a number of shortcomings that do not make it possible to call any of these memory options universal. If we add here the problem of colossal data growth all over the world and the thirst of mankind for energy conservation, then it is necessary to create something completely new. Today we will meet with a study in which scientists introduced a new type of memory that combines the advantages of both flash and DRAM memory. What “goodies” does this innovation have, what technologies were used to create it, and what are the prospects? We learn about this from the report of the research group. Go.

Study basis

There are many types of memory, and all of them were created for a specific task: SRAM (static random access memory) for cache, DRAM (dynamic random access memory) for active memory, flash memory for data storage, etc. However, as expected, each of the above types of memory has its own personal flaws.

For example, flash memory, which is a collection of MOS transistors (metal oxide semiconductor) with a floating gate (FG) for storing charge. The data are presented in such an embodiment as the amount of charge held in the FG, which is isolated by oxide layers.

The disadvantage, according to scientists, is that for recording and erasing, a sufficiently large voltage is required for control by a control shutter (CG), usually around ± 20 V2 . This process is slow, and the failure mechanism induced by a power surge leads to a reduction in the life of the device.

Despite this minus, there is a rather impressive plus - data is read by checking the channel conductivity, which requires very little voltage. Due to this, the data remains intact, which is called non-destructive reading.

DRAM, in turn, is much faster than flash memory, which is why it is used for active computing processes, so to speak. The disadvantage of DRAM is that data is lost from the cells when it is read. In addition, charge leaks from capacitors used to store data occur.

SRAM is also a fairly fast memory type and data is not as lost as in DRAM. However, as a rule, 6 transistors per cell are used, that is, you need a lot of area on the chip.

Having presented the above-described shortcomings of the classical types of memory, scientists emphasize the importance of finding an alternative or hybrid option that will be free from such problems, while combining all the advantages of their predecessors.

In this work, researchers present to their attention their vision of a new type of memory - a new low-voltage, semiconductor, charge-based, non-volatile memory device of a compact form, operating at room temperature. Researchers dubbed their offspring a “universal memory” (simple, but tasteful).

The device is a memory with a floating gate, created on the basis of InAs / AlSb / GaSb heterostructures, where InAs is used both as a floating gate and as a channel without transitions.

Scientists have provided simulation and actual test results for a single-cell prototype.

Research results

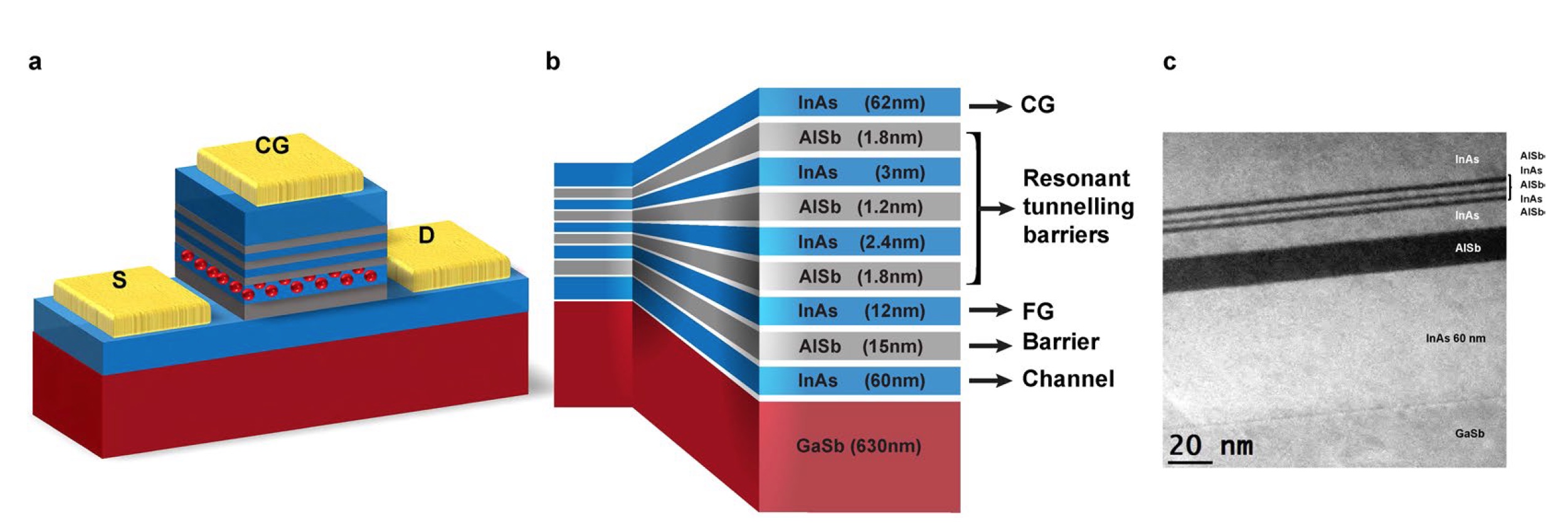

Image No. 1

The image above shows a schematic view of the device and a picture of a PREM (transmission scanning electron microscope).

As in the case of flash memory, in this device the charge is stored in FG, but at the same time there are no oxide barriers. Instead, a shift of the conduction band in the so-called 6.1-Å family of semiconductors was used. That is, the device underlying the memory cell is more like a high electron mobility transistor (HEMT) than a MOS transistor. InAs forms a channel that does not contain transitions. However, n-doping was used in order to compensate for unintentional background doping and to keep Ga vacancies in the underlying GaSb. Both of these tasks naturally make p-type layers.

pn junction * is the contact area of two semiconductors with different types of conductivity - p (hole) and n (electronic).

Image No. 2

Graph 2a shows the simulated alignment of energy bands, as well as the density of electrons and holes in the layers in the absence of bias. The theoretical data, together with the simulation, demonstrate that the InAs conduction band is below the GaSb valence band at the InAs and GaSb interface. And this leads to the transfer of electrons from the GaSb layer to the InAs layer, after which holes remain in GaSb.

The hole * is an unfilled valence bond, manifesting itself as a positive charge equal to the charge of an electron.The accumulated electrons / holes are visible at the interface between InAs and GaSb, but the electrons in the InAs channel are not connected to the InAs / GaSb interface, and their density is observed throughout InAs. The conductivity of the entire channel is dominated by electrons in InAs, which will have higher mobility and higher density than holes in GaSb.

The internal FG of the InAs layer is isolated from the InAs channel by an AlSb barrier (15 nm). At the same time, double * InAs quantum wells and three AlSb barriers act as a resonant tunneling barrier between FG and CG InAs with n-doping.

Quantum well * - limits the movement of particles in the two-dimensional dimension (instead of three-dimensional), because of which they can only move in a flat layer.Therefore, in the device under study, the electrons stored in the FG of the InAs layer are isolated by an anomalously large gap in the conduction band with AlSb. This means that you can get a charge limiting system, which will have a storage time at room temperature equal to 1014 years.

The most important aspect of the operation of the device under study is the fact that two quantum wells (QW1 and QW2) in the triple resonant tunneling barrier have different thicknesses, i.e., limited states with different energies take place ( 2a) Since QW2 is thinner than QW1, the only available energy level for electrons in QW2 has higher energy than the equivalent in QW1. In addition, the state in QW1 has a significantly higher energy than the state in the neighboring CG region. This prevents direct electron tunneling between CG and FG, and the electron transfer barrier from CG to FG (or vice versa) is determined by a shift of the InAs / AlSb conduction band by 2.1 eV, i.e. the charge will not flow to / from FG.

The ground and primary excited states in the floating gate (FG) are located well below the energy states inside both QWs. Therefore, when no voltage is applied, the electrons are locked inside the FG, i.e. the triple resonant tunneling barrier becomes insurmountable for electrons to / from FG. Thus, non-volatility is achieved.

If an insignificant voltage is applied to the control gate (CG), then it is possible to adjust the coupling of energy states inside the resonant tunneling barrier, which will allow the electrons to freely pass from ( 2b ) or ( 2c ) the floating gate.

During the experiments, all read, write, and erase operations were carried out in several cells (shutter size 10 x 10 μm) in a dark box protected from electrostatics at room temperature. All operations, including recording and erasing, were performed at an offset of ≤ 2.6 V, which is approximately an order of magnitude lower than necessary for full operation with a flash memory cell, the researchers emphasize. Erasing was performed by shifting the control gate (V E CG-S ) by +2.5 or +2.6 V between the CG and the source, which led to the state “0”.

In image 2bShown is the simulated alignment of energy bands obtained with an erasure voltage of +2.6 V. Under such circumstances, the calculated electron energy level in QW1 is lower than the level in QW2, while both are below the first excited state and are close to the energy level of the ground state in FG. The result is an erasure, i.e., an electron flux from FG to CG followed by depletion of FG. The same principle works for the write operation: V W CG-S = -V E CG-S to increase the charge in FG (state “1”).

Chart 2c is a simulated energy zone when the control gate offset is used to record data: V W CG-S= −2.6 V. In this case, the energy levels in QW1 and QW2 practically coincide, which leads to a strong coupling of these states, resonant tunneling, and the electron flux from CG to FG.

Due to capacitive coupling, the channel conductivity depends on the amount of charge stored in the FG, therefore, data is read by measuring the gate-source current at a fixed gate-source voltage.

Charge increase in FG, i.e. state "1", reduces the charge in the channel, which leads to a decrease in its conductivity. In the case of the state “0”, the reverse process occurs. Data can be read without any bias to CG, but voltage is necessary for individual selection of devices in an array of cells. In addition, the voltage should generate an electric field through the resonant tunneling barrier, which will make it possible to transfer the charge from / to FG. To achieve these tasks, only ~ 2.5 V. is required.

Universal Memory Features

During practical tests, reading was performed with a zero offset by CG and V S-D = 1.0 V. However, according to scientists, it was possible to apply less voltage for a successful reading.

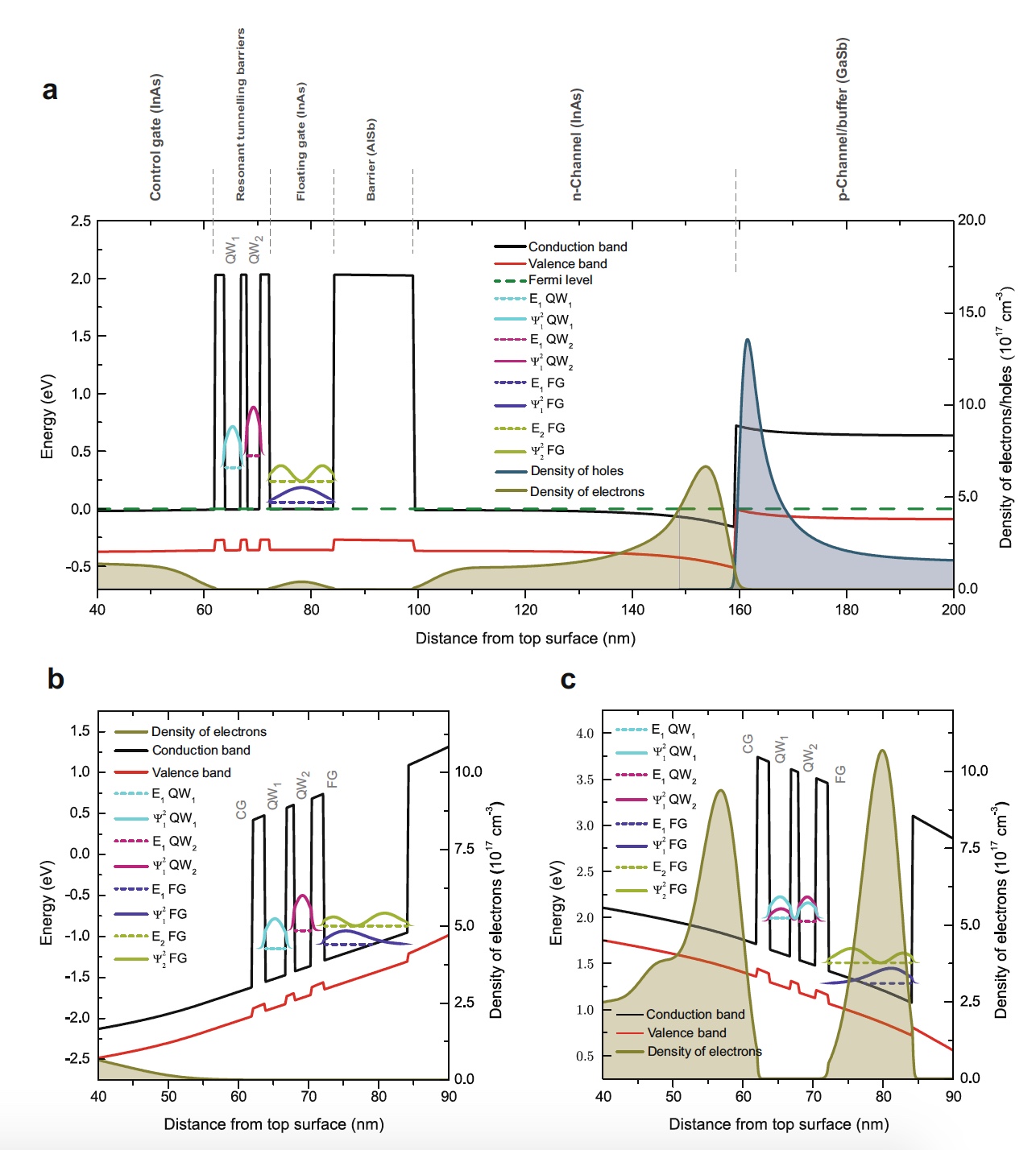

Image No. 3

Image 3a shows the erase-read-write-read process. The main feature of the sequence is the read operation after each erase or write step.

Figure 3b shows a more complicated sequence in which after each erase and write operation there is not one read operation, but several. In this way, the researchers demonstrate that the read operation is non-destructive.

Between the state “0” and “1” there is a clear difference in all sequences. However, on 3b there are signs of a symmetric upward shift in I S-D as the number of operations increases. While the reason for this behavior is unclear, but scientists intend to explore this aspect in further works. But on 3a this is not observed, since the voltage for erasing / writing is slightly lower.

After several hundred write and erase operations, as well as many read operations during several practical tests, scientists did not find any signs of damage to the device.

An important feature of all types of memory, which are based on charge storage, is the switching energy determined by the charging energy of the capacitor.

The similarity of the fundamental principles of flash memory technology and the universal memory under study suggests a comparison of these two types of memory. If we assume that the two devices of these two types have the same capacity with the same shutter size, then the switching energy of the universal memory will be 64 times less than that of flash memory. These amazing numbers also show the superiority of universal memory over DRAM.

According to theoretical estimates, the CG-FG capacitance is of the order of 10 -12 F for a device measuring 10 x 10 μm, and the switching energy is approximately 2 x 10 -12 J. Reducing the physical size of the device sharply reduces the switching energy to 10 -17J for a device with a size of 20 nm, and this is 100 times smaller than for DRAM, and 1000 times smaller than for flash memory. And this, according to the bold statements of the researchers, is very unique characteristics.

Image 3c shows some write-erase operations from 3b , where the differences between state “0” and “1” are visible: consecutive read measurements after erasure give slightly lower I S-D for state “0”. The opposite situation is observed with sequential read measurements after writing, or rather, I S-D is slightly larger.

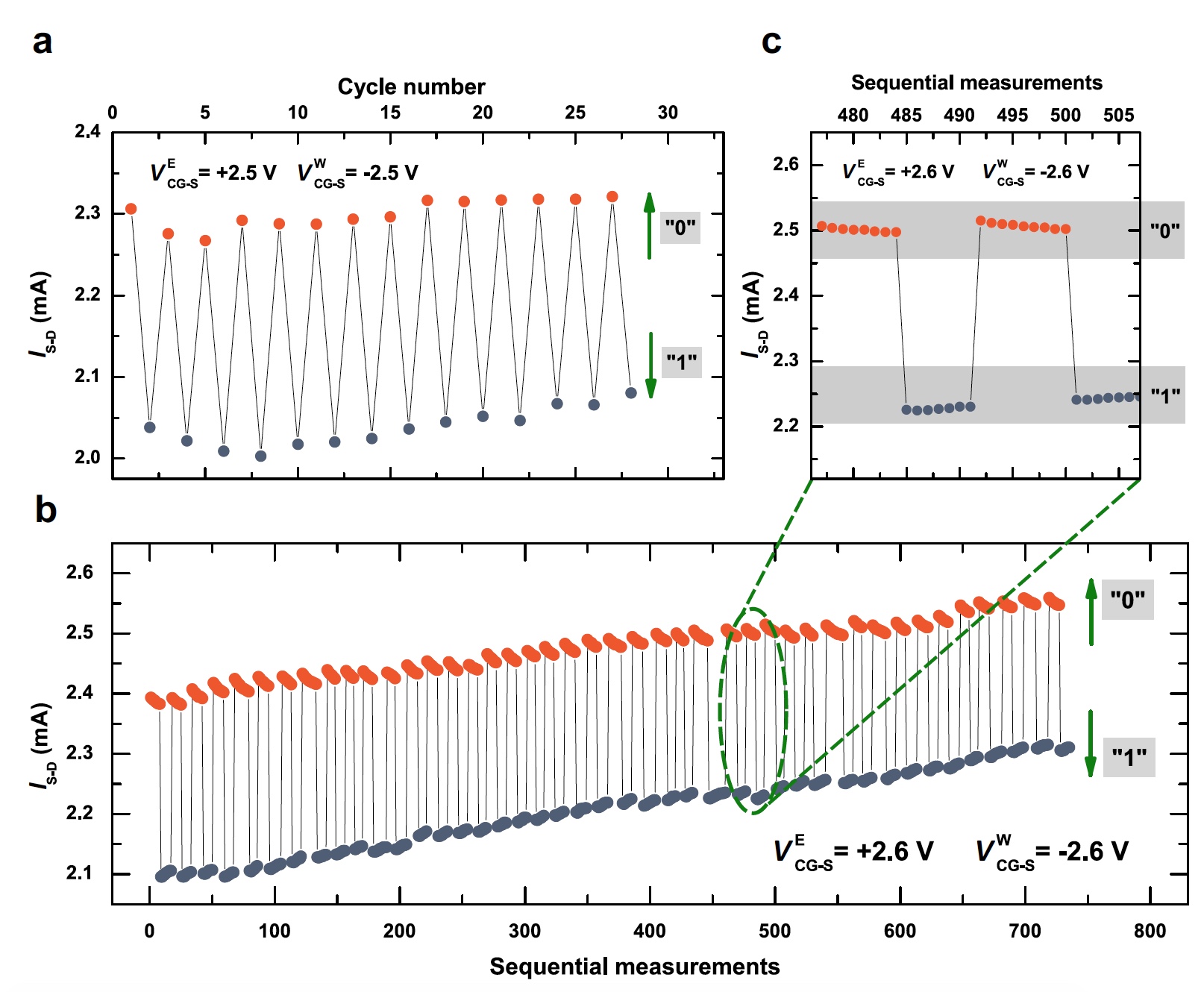

Scientists attribute this effect to the variability (volatility) of the data. To study this, scientists performed a sequence of read operations over a long period of time for each state of memory (image No. 4).

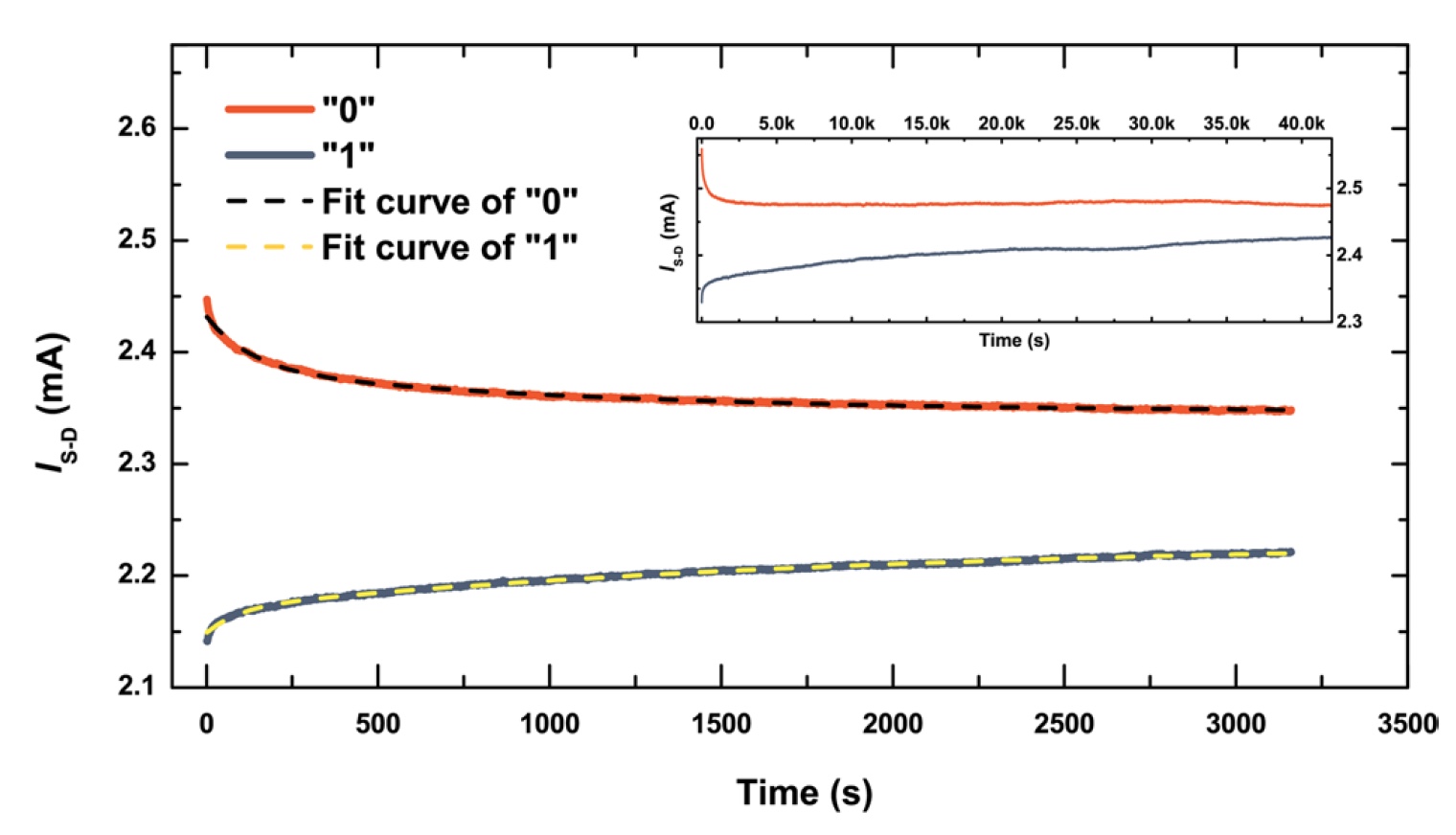

Image No. 4

Both states “0” and “1” showed an initial fast decay, which is consistent with what is seen for 3s . But after this, much slower changes occur, so that during the entire time of observation the corresponding states “0” and “1” are clearly distinguishable.

Another experiment was also carried out (insert on image No. 4), which shows the limiting saturation of exponential attenuation and distinguishable states “0” and “1” in time.

The existence of double exponential attenuation means that several mechanisms underlie degradation of states at once. Among the possible options, scientists distinguish tunneling through defective states in AlSb barriers, thermal excitation of electrons through the narrow InAs band gap, and recombination with thermally generated holes.

Evaluation of the capacitance of the device and the applied voltage for recording / erasing indicates that approximately 107 electrons are transferred from / to the floating gate during the writing and erasing operation. This is quite a lot, but practically no negative influence is observed.

For a more detailed acquaintance with the nuances of the study, I recommend that you look into the report of the research group .

Epilogue

Scientists managed not only to develop a new type of memory, but also to conduct successful first practical tests of a non-volatile, charge-based device of a compact size at room temperature. Scientists also managed to combine non-volatility and low-voltage switching by the quantum-mechanical properties of an asymmetric triple resonant tunneling barrier. Researchers say that their device can be scaled without losing its dignity.

Times are changing, so are technologies. Flash memory, SRAM, and DRAM have long held a dominant position among memory devices, but this could change if the development of universal memory continues with the same success as in this study. This technology will greatly reduce the power consumption of devices equipped with it, as well as extend their service life and increase productivity.

Further studies planned by the authors will show how revolutionary memory is, so proudly called universal by scientists.

Thank you for your attention, remain curious and have a good working week, guys!

Thank you for staying with us. Do you like our articles? Want to see more interesting materials? Support us by placing an order or recommending it to your friends, a 30% discount for Habr users on a unique analogue of entry-level servers that we invented for you: The whole truth about VPS (KVM) E5-2650 v4 (6 Cores) 10GB DDR4 240GB SSD 1Gbps from $ 20 or how to divide the server? (options are available with RAID1 and RAID10, up to 24 cores and up to 40GB DDR4).

Dell R730xd 2 times cheaper? Only we have 2 x Intel TetraDeca-Core Xeon 2x E5-2697v3 2.6GHz 14C 64GB DDR4 4x960GB SSD 1Gbps 100 TV from $ 199 in the Netherlands! Dell R420 - 2x E5-2430 2.2Ghz 6C 128GB DDR3 2x960GB SSD 1Gbps 100TB - from $ 99! Read aboutHow to build the infrastructure of the building. class using Dell R730xd E5-2650 v4 servers costing 9,000 euros for a penny?