Microelectronics technologies on the fingers: Moore’s Law, marketing moves and why nanometers are not the same now. Part 2

- Transfer

In the first part, we briefly examined silicon physics, microelectronics technology, and technological limitations. Now let's talk about physical limitations and physical effects that affect the sizes of elements in a transistor. There are many of them, so let's go through the main ones. Here you have to get into physics, otherwise nothing.

Disclaimer: Once upon a time I dabbled in writing articles about chip manufacturing , and in the series of articles “Inside Look” I even looked inside of them, i.e. The topic is extremely interesting to me. Naturally, I would like myselfthe author of the original article published it on Habré, but in connection with employment, he allowed me to transfer it here. Unfortunately, the Habr rules do not allow direct copy-paste, so I added links to sources, pictures and a little gag and tried to straighten the text a little bit. Yes, and I know and respect articles ( 1 and 2 ) on this topic from amartology .

Physical effects in microelectronics

The order of the basic quantities for silicon

The concentration of silicon atoms in the crystal is 10 22 cm -3

The concentration of intrinsic electrons and holes at room temperature is 10 10 cm -3

The concentration of impurity atoms from lightly doped regions is 10 16 -10 18 cm -3

The concentration of impurity atoms from lightly doped regions is 10 19 - 10 20 cm -3

The concentration of impurity atoms in very heavily doped regions is 10 21 cm -3 . In this case, we are talking about a degenerate semiconductorsince such a concentration (one impurity atom per 10 or less silicon atoms) changes the energy structure of the crystal.

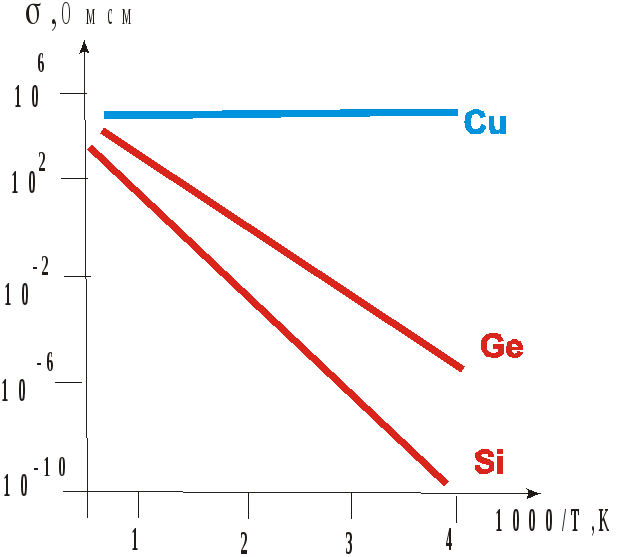

Temperature dependences of silicon characteristics

From the first part we remember that at room temperature pure silicon is a dielectric. An electron-hole pair arises in only one of a trillion cases, but this fraction increases exponentially with increasing temperature. There is such a thing - the temperature of doubling the concentration of own charge carriers. For silicon, it's about 9 degrees.

Those. increase the temperature by 9 degrees, the percentage of decaying silicon atoms increases by 2 times; 18 degrees - 4 times; 27 degrees - 8 times; 36 degrees - 16 times; 45 - 32 times; 90 - 1024 times; 180 - 10 6 times; 270 - 10 9 times.

Comparison of the thermal conductivity of copper, silicon and germanium. A source

We get that when heated to 200 degrees (~ 2.1 in the graph above), the intrinsic concentration of electron-hole pairs becomes 10 16 , which is equal to the impurity concentration of lightly doped layers. At 300 degrees (~ 1.75) already 10 19 , this is the concentration of heavily doped layers (n + and p +). At this temperature, silicon actually turns into a conductor and transistors lose controllability.

Problems will begin much earlier. The temperature in the chip is uneven. There are local heating zones, usually in the middle of the chip. If the temperature in a small area exceeds 200 degrees, then due to an increase in the intrinsic conductivity of silicon, the leakage current begins to increase. This leads to even more heating, and this further increases the leakage current and expands the area of overheating. The process becomes irreversible and ... boom. And irrevocably. Therefore, on all large microcircuits, automatic protection against overheating is set.

That is why it is so important not to allow strong heating of the crystal.

For comparison, in gallium nitride at room temperature, the concentration of intrinsic electrons and holes is several orders of magnitude lower, and the temperature of doubling the number of intrinsic charge carriers is about 25 degrees. The problems described above in gallium nitride begin at about 600-700 degrees.

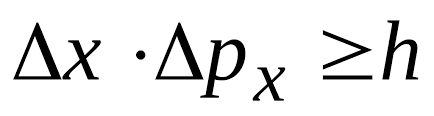

Tunnel current

This phenomenon is both complex and simple at the same time. The roots lie in the quantum nature of the electron. An electron lives by the laws of quantum mechanics, which are not always understood from the point of view of classical physics. According to these laws, an electron is not only a particle, but also a wave, and its behavior can be calculated only with some probability. There is such a Heisenberg formula:

It is also called the Heisenberg uncertainty relation. It follows from the formula that the spatial parameters of the electron cannot be determined with an accuracy greater than a certain value (Planck's constant). In extreme cases of the equation, if we know the exact location of the electron, we will not know anything about its speed and direction of motion. If you know the speed and direction exactly, then nothing will be known about his whereabouts. It turns out that the electron is such a particle blurred in space with peaks of probability of being. At any moment, an electron can be anywhere in the Universe without any external influence. True, the probability of its appearance is very far from the current location is vanishingly small.

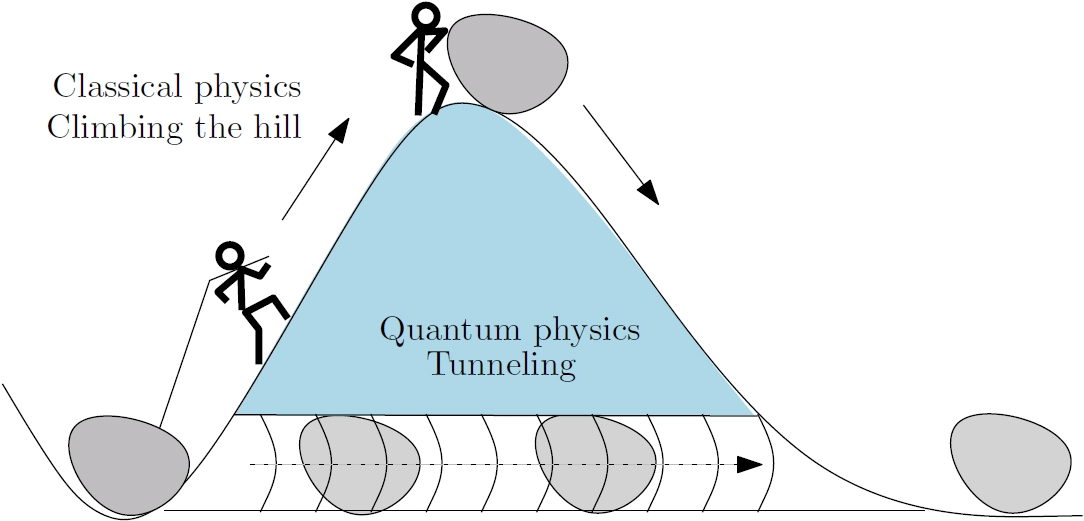

Now imagine the structure of the Metal - Dielectric - Semiconductor n-type (MIS). In a metal, the concentration of free electrons is approximately equal to the concentration of atoms (10 22 / cm 3 ). They cannot penetrate into a dielectric, because for electrons from a metal this is a region of forbidden energies. Inside the dielectric, an electron wave with energy as in a metal will begin to interfere (self-destruct itself). But they can materialize in an n-type semiconductor, where for them there is a zone of allowed energies. Electrons pass from a metal to a semiconductor through an oxide layer without any external influence, simply because of their probabilistic nature. This is the tunnel current . The process itself is called tunneling, or quantum tunneling (sounds cooler!).

The additional energy that would have to be added to the electron for “classical” penetration into the oxide is called the potential barrier. Schematically, an electron gnaws through a tunnel through a potential barrier.

There is a flow in the opposite direction - from a semiconductor to a metal. But since the concentration of free electrons in the semiconductor is several orders of magnitude lower, the reverse flow is proportionally smaller.

A p-type semiconductor for electrons from a metal is also a band of forbidden energies. However, the reverse process is possible here — the tunneling of valence electrons from a semiconductor to a metal with the appearance of holes in silicon. It looks like holes are tunneling from metal. The intensity, other things being equal, is about 10 times lower than the tunneling of free electrons.

The tunneling current for distances above 1 μm can be neglected. Too low probability and transitions too rare. As the distance decreases, the probability of spontaneous transitions increases sharply. At distances of units of nm, the tunneling current grows 10 times when approaching 0.2 nm.

A similar mechanism works for npn silicon layers. For a free electron from the n-region, the p-region is a band of forbidden energies, no transitions occur. But if the width of the p-base is set too narrow, the electrons begin to tunnel directly from source to sink. This limits the theoretical maximum base width to 8 nm. At smaller sizes, due to the tunneling current, the source - drain transistor becomes in principle uncontrollable.

For pnp structures, the situation is similar, but holes (valence electrons) tunnel.

In degenerate semiconductors (heavily doped) in the band of forbidden energies there are islands of allowed energies. For them, the option of tunneling through these islands is possible. About how to overcome a stream by jumping on sticking boulders.

Space Charge Region (SCR)

The space charge region (SCR), it is also the depletion region, it is also the space charge region - it is an electrically charged layer that forms at the boundary of n and p regions.

Mentally connect 2 pieces of silicon, one n-type, the other p-type. In the n-layer there are many free electrons, in the p-layer there are many holes; they move randomly. Part of the free electrons goes to the p-layer, part of the holes to the n-layer. As a result, uncompensated positive ions remain in the n-layer, and negative ions are not compensated in the p-layer. A local electric field appears along the boundary of the regions, which begins to impede further transitions. The field strength is maximum at the boundary, and gradually decreases with distance. In the end, the field strength becomes such that the transfer of holes and electrons ceases and an equilibrium state is established. For silicon, the voltage of such an internal field is about 0.5 volts. Depends on the impurity concentration on both sides. The dependence is weak, about 0,

In addition to the appearance of an electric field at the boundary, there is a decrease in the concentration of free electrons and holes. Directly at the boundary of the layers to zero. Hence the second name - “depleted region”. The width of this region depends on the voltage at the transition and the concentration of impurities. The dependence on the concentration of impurities is inversely quadratic, i.e. with an increase in concentration by a factor of 100, the width of the SCR decreases by a factor of 10 (actually, slightly less, because the voltage at the junction increases).

This is a state where external voltage is not applied to the structure.

If you apply an external voltage, then it is vectorized with the internal.

We apply a small forward voltage to the junction, i.e. plus (+) to the p-layer, minus (-) to the n-layer. The external and internal fields are directed in different directions and begin to compensate each other. Transition voltage and SCR width are reduced. When the voltage of the external field becomes higher than the internal, the SCR disappears, the pn junction opens completely. For semiconductor diodes there is even such a parameter - threshold voltage. This is the forward voltage at which the diode opens completely.

Now apply the reverse voltage: minus (-) to the p-layer, plus (+) to the n-layer. The external and internal fields add up, the voltage at the junction and the width of the SCR increase.

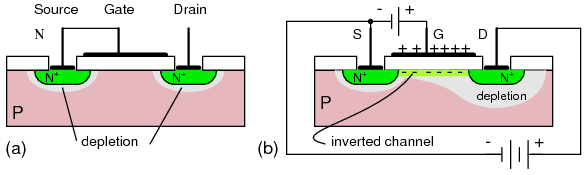

If we transfer this model to our field effect transistor, we get the image below:

The depleted areas (SCR) are indicated by light pink. We get that the real widththe active base , which is controlled by the gate voltage, is less than the source-drain distance. That is, the size of the base minus the width of the SCR transitions. In the absence of supply voltage, the width of the SCR of the source and drain are the same. If you apply the operating voltage, the width of the SCR of the drain increases, since it is under reverse bias. The active base narrows even further:

If the base is too short, the SCR of the drain and the source are connected. The width of the active base becomes 0, a through current flows from the drain to the source, the transistor opens. Regardless of the voltage on the shutter. The transistor becomes uncontrollable. The effect is called “base puncture” ( note: as F376 correctly noted , most likely, we are talking about “base breakdown”).

There is still an intermediate option when the SCR does not close, but the distance from the source to the boundary of the SCR of the runoff is less than 8 nm. Then, in the SCR, electrons begin to tunnel from the source. Once in the SCR, they are thrown into the drain by an electric field. Simply put, a decent tunneling current will flow from source to drain.

Avalanche breakdown

If the electric field inside the SCR becomes too high, then an electron that accidentally flies into it accelerates so much that it removes the electron from a neutral atom. 2 electrons appear, they again accelerate and strip off the electrons from the following, etc. The process resembles an avalanche, hence the name. A conductive channel appears in the SCR through which current flows. The transistor opens spontaneously.

A similar situation can occur in the gate dielectric. If the field strength is above the threshold, a “fast” electron flying out of the metal accelerates and causes an avalanche.

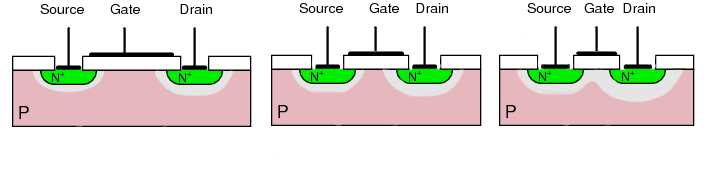

A clear comparison of different types of breakdown. A source

To avoid such an avalanche breakdown, it is necessary to prevent excess field strengths above the breakdown value. Field Strength = Stresses / Length. Those. it is necessary to reduce the voltage and increase the width of the SCR (or the thickness of the dielectric).

Electrical resistance areas

This is already a classic electrical engineering. And the drain, and the source, and the channel, and even the conductive metal tracks have their own electrical resistance. The resistance is higher, the greater the length of the plot and the smaller the cross-sectional area.

Suppose we all the elements of the transistor proportionally reduced by 2 times. By reducing the length, the resistance of the section is reduced by 2 times , and by reducing the width and height increases by 4 times . In total, this gives an increase in the resistance of the element by 2 times . With the passage of current, the resistance causes a voltage drop. For transistor voltages in the region of 1 V and below, even a small voltage drop will be critical.

For metallization, this question was solved simply - the first narrow layer of metal connects only the elements inside the cell. Everything else is brought to the upper levels of metallization: there the oxide layer is made thicker and the tracks wider. Nevertheless, the size of contact windows and metallization tracks cannot be infinitely reduced.

For areas of silicon, an increase in resistance was compensated by an increase in the concentration of impurities. At least until recently, until the effects of tunneling and breakdown began to affect.

Another way was the technology of “stretched silicon”, or “strained silicon”. Its essence is that a layer of germanium is deposited on a silicon substrate. Germanium is an element of the same group as silicon, similar in crystal structure. However, germanium atoms are larger, respectively, the distance between them in the crystal lattice is greater. Then, a thin epitaxial silicon film is formed over germanium. Silicon in the film begins to repeat the crystalline structure of germanium, the step of the crystal lattice will be both in germanium and greater than in ordinary silicon. It turns out that silicon is, as it were, stretched in all directions. Hence the name. This gives an increase in the mobility of electrons and holes.

The combined effect of physical effects

Now consider the effects of these effects together.

The main threat in the miniaturization of transistors is a puncture base. To remove it, you need to reduce the width of the SCR. It can be reduced by reducing external stress and increasing the concentration of impurities in the base.

The supply voltage has nowhere to reduce, it is already in the region of 1V - about two thresholds. If we do even less, then we risk getting a “slurred" opening of transistors due to electrical resistance.

You can increase the concentration of impurities in the database, but then we get:

- a sharp increase in the tunneling leakage current from the drain to the base;

- increased risk of getting an avalanche breakdown of the transition;

- increasing the voltage threshold for inducing the channel, with the risk of getting a breakdown of the gate dielectric.

Due to these limitations, the concentration of impurities in the base is fixed at 10 18 -10 19 .

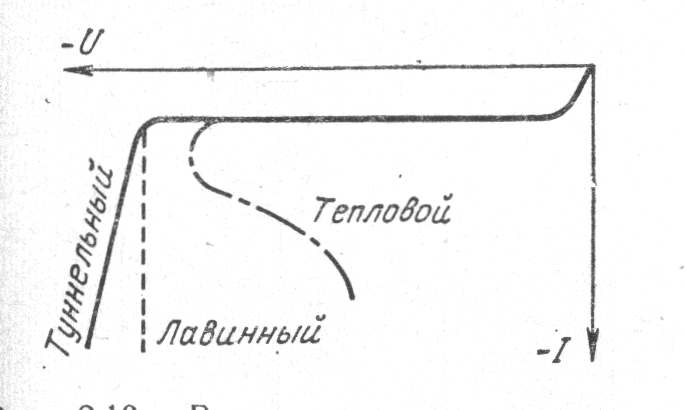

All these and unnamed factors restrict the minimum base width for silicon MOS transistors in the region of 25 nm . It is possible less, but the leakage current becomes inadequate and the probability of failure increases exponentially.

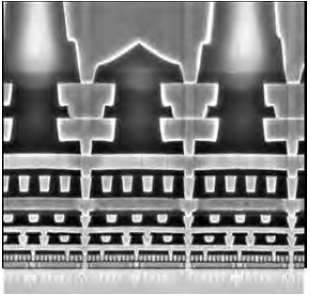

Micrograph of transistors made on 90 nm and 32 nm process technology. Zoom and scale are identical. Source

As we can see, the size of metal contacts has become much smaller, but the width of the base has not changed. All the same 25 nm. Moreover, for transistors using the technology of 14 nm, 10 nm and 7 nm, it is the same ( ooops! ).

This was first encountered when moving from 130 nm to the first 90 nm series. Then for the first time they could not reduce the width of the base in proportion to all other sizes, it remained approximately 35 nm. Later, it was still reduced to 25 nm, but since then the width of the base has no longer been subject to the proportions of technology. And the smaller the transistors became, the more this manifested itself.

It was necessary to change the criteria of technical processes. What have you done? Most did nothing. They continued to issue photolithography permission as the norm of the technological process. Or the minimum width of the metallization path as a manifestation of the most simple and intuitive operation. And here we come to the m and rketingu ...

The most creative marketers came from Intel. They began to calculate the technical process rate from the size of the elements, for example, based on the area of the six-transistor cell of static memory. In technology with a resolution of 65 nm lithography, it was 0.77 μm 2 , and at a resolution of 40 nm it became 0.37 μm 2 . If the transistor sizes were reduced proportionally as before, then this corresponds to the technology of 45 nm. So we will assume that we have 45 nm technology. This is where the discrepancies between Intel technology and others came from - 28 nm for all, 32 nm for Intel; 20 nm for all, 22 nm for Intel; 10 nm for all, 14 nm for Intel.

As subsequent history showed, Intel ended up being more honest than its competitors.

Effect of leakage currents

There is a wonderful graph from an article already in 2010:

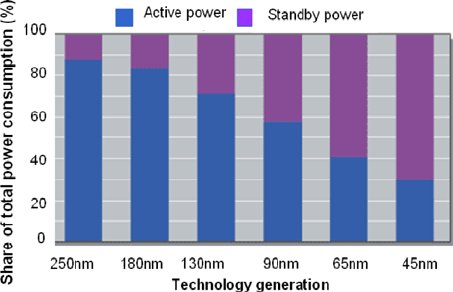

Source The

graph shows the percentage of working and spurious energy consumption. Blue - energy release as a result of recharge currents (operating current), purple - the result of leakage currents (stray current). This is taking into account the measures that have been taken to reduce stray currents.

The reason why the growth of processor clock speeds stopped is clearly visible. The first processors in 3 GHz ( Pentium 4 , for example) appeared in the early 2000s. So at this level and stayed. Usually this is explained by the fact that the number of cores has increased, the logic has become more complicated, pipelining has deepened, so the requirements for stability and, in general, happiness in gigahertz have grown. Partly true. But!Previously, they somehow managed to combine all these factors with an increase in frequencies.

The fact is that earlier, with a decrease in the size of transistors, a reserve for energy consumption appeared. For example, the technological norm decreased by 2 times, the number of transistors increased by 4 times, and the average power consumption of each transistor decreased by 6-7 times. The fact is that CMOS transistors consume current when switching, and the increase in the number of transistors was mainly due to the increase in cache memory. Memory transistors switch relatively rarely. Therefore, they consumed less than the active elements of the processor.

This difference made it possible to raise the clock frequency with the same heat.

On going from 180 nm to 130 nm, the leakage current ate this delta. Since then, despite all the tricks, they have not come out in plus. All

In fact, during the 2000s, a quiet glanders occurred a change of priorities. Previously, the priority was to reduce the size of transistors, now - to reduce leakage.

About Leak Control Techniques

Subgate Oxide Material Change

With the switch to High-k, dielectrics also had to change the gate material. Instead of polysilicon, they began to reuse a metal, usually nickel silicide NiSi. Silicon oxide is still used for separation with the second and further metallization layer.

Briefly about High-k dielectrics

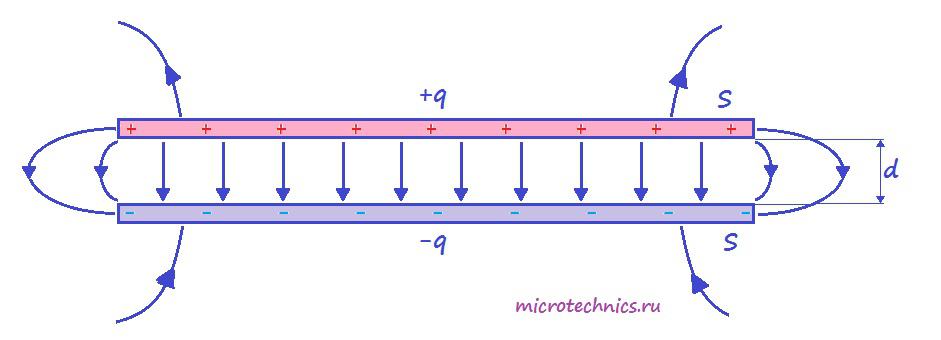

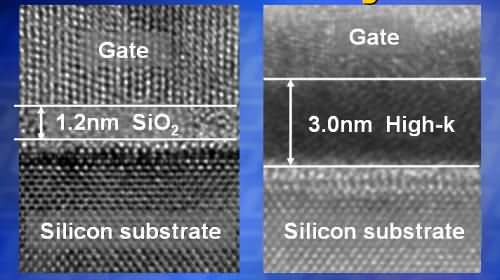

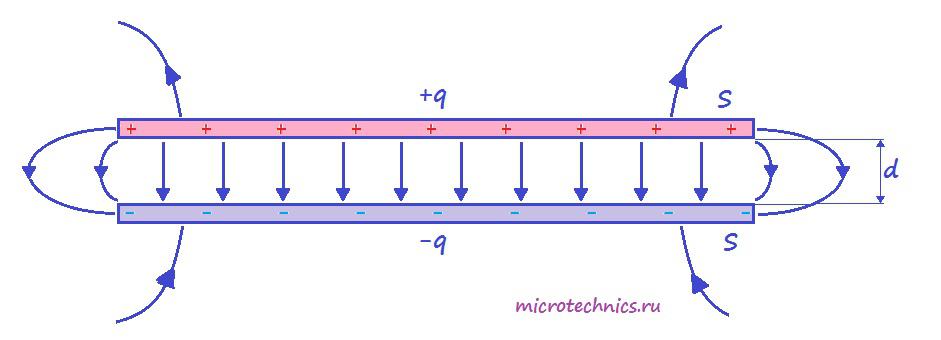

One of the ways to improve the parameters of transistors was to reduce the thickness of the gate dielectric. There are many reasons. I won’t go into physics, it’s already too much. In short, I will say that there is such a parameter as the shutter capacity. The gate – dielectric – silicon system resembles a model of a flat capacitor familiar from the course of school physics.

The main parameter of the capacitor is capacitance. This is the ability of one plate to change the electrical state to a second without direct electrical contact. Unlike stray containers, shutter capacity is a useful thing. It characterizes the shutter's ability to quickly induce a channel and collect as many charge carriers in the surface layer as possible. This minimizes the electrical resistance of the channel and the voltage drop. The capacity is determined by the formula:

S is the area of the plates,

d is the distance between them,

ԑ is the dielectric constant of the material between the plates, for vacuum 1, almost 1 air,

ԑ 0 is the dimensional constant.

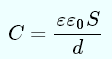

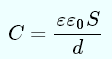

As the size shrinks, the effective shutter area decreases. To compensate for it, the thickness of the gate oxide was reduced. As a result, we came to a thickness of 1.2 nm ( sic! ). These are 6 (!!!) atomic layers. At the same time, they got a decent tunneling leakage current from the gate to silicon. The next step was to reduce the thickness to 5 atomic layers, i.e. up to 1 nm, with an increase in the tunneling current of 10 ( !!!) times (with such dimensions, the probability of tunneling increases by a factor of 10 when approaching 0.2 nm). Such leakage currents put an end to the stable operation of the chip.

Therefore, we used the third component of the equation, the dielectric constant of the gate insulator. I had to abandon the correctly served silicon oxide in favor of materials with a higher dielectric constant - High-k dielectrics. Usually it is hafnium oxide HfO 2 or tantalum oxide Ta 2 O 5 . The dielectric constant of silicon is 3.9, for High-k dielectrics 25-30. To ensure the same capacitance and the same distribution of tension in the base, it is possible to use a dielectric layer much thicker, because of which the tunneling currents from the gate are reduced by orders of magnitude.

The main parameter of the capacitor is capacitance. This is the ability of one plate to change the electrical state to a second without direct electrical contact. Unlike stray containers, shutter capacity is a useful thing. It characterizes the shutter's ability to quickly induce a channel and collect as many charge carriers in the surface layer as possible. This minimizes the electrical resistance of the channel and the voltage drop. The capacity is determined by the formula:

S is the area of the plates,

d is the distance between them,

ԑ is the dielectric constant of the material between the plates, for vacuum 1, almost 1 air,

ԑ 0 is the dimensional constant.

As the size shrinks, the effective shutter area decreases. To compensate for it, the thickness of the gate oxide was reduced. As a result, we came to a thickness of 1.2 nm ( sic! ). These are 6 (!!!) atomic layers. At the same time, they got a decent tunneling leakage current from the gate to silicon. The next step was to reduce the thickness to 5 atomic layers, i.e. up to 1 nm, with an increase in the tunneling current of 10 ( !!!) times (with such dimensions, the probability of tunneling increases by a factor of 10 when approaching 0.2 nm). Such leakage currents put an end to the stable operation of the chip.

Therefore, we used the third component of the equation, the dielectric constant of the gate insulator. I had to abandon the correctly served silicon oxide in favor of materials with a higher dielectric constant - High-k dielectrics. Usually it is hafnium oxide HfO 2 or tantalum oxide Ta 2 O 5 . The dielectric constant of silicon is 3.9, for High-k dielectrics 25-30. To ensure the same capacitance and the same distribution of tension in the base, it is possible to use a dielectric layer much thicker, because of which the tunneling currents from the gate are reduced by orders of magnitude.

Silicon on the insulator (SOI)

Silicon technology on an insulator , aka SOI, aka SOI, has been used before to isolate cells. Here we go even further: an oxide layer is formed on top of the silicon substrate, and a silicon layer is epitaxially grown ( UPD: the author, apparently, has slightly simplified the SIMOX and Smart Cut process ).

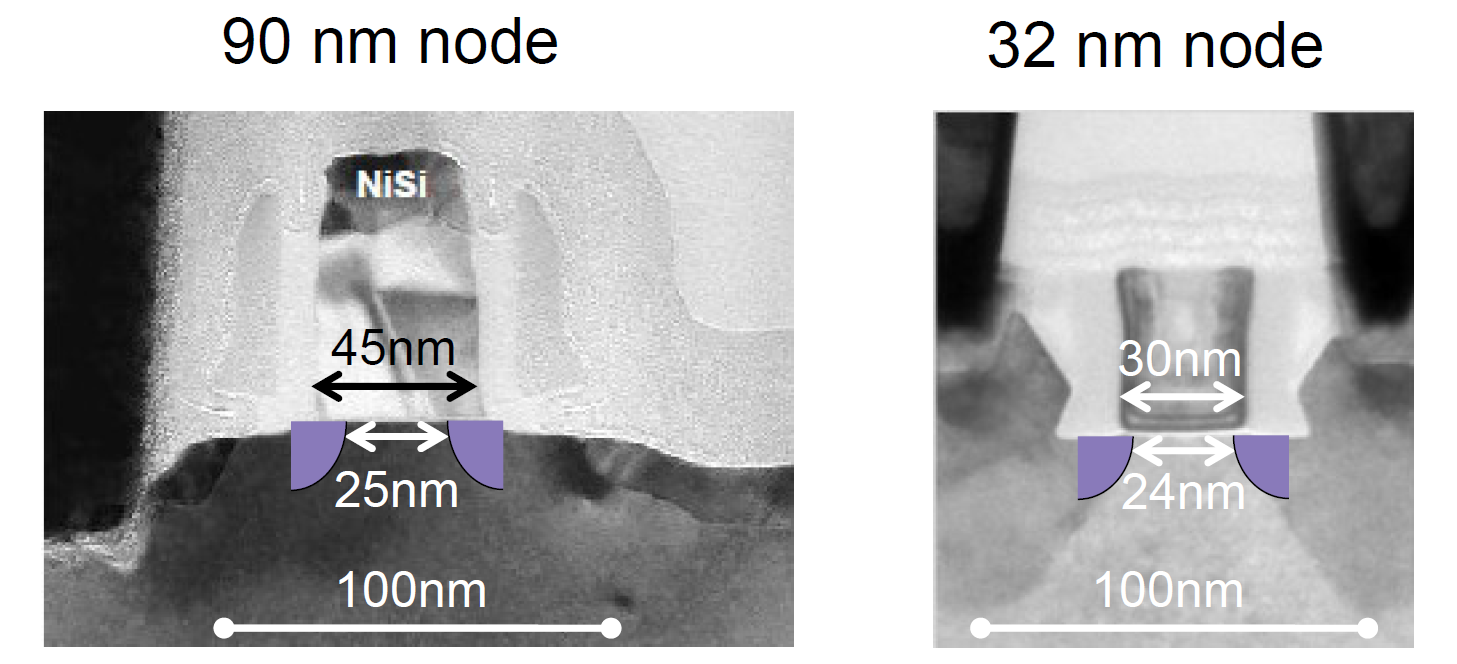

Schematically, the difference between SOI technology and conventional planar MOS

This technology dramatically reduces leakage currents.

But there are also disadvantages. SOI technology is still very complicated and expensive. In addition, due to the thin isolated base, there are problems with the accumulation of a sufficient number of electrons or holes to form a channel. The channel is very narrow. Another problem is heat dissipation. Silicon oxide has a low thermal conductivity, and heat removal from the film to the mass of the substrate is difficult.

Alternatively, instead of silicon oxide, sapphire Al 2 O 3 can be used ; its thermal conductivity is higher. Ideally, the oxide should be under the drain and source, but it would not be under the base. Then, in combination with a High-k dielectric, it would be possible to increase the concentration of impurities in the base and reduce the channel width to 15 nm. However, while the use of this technology is limited.

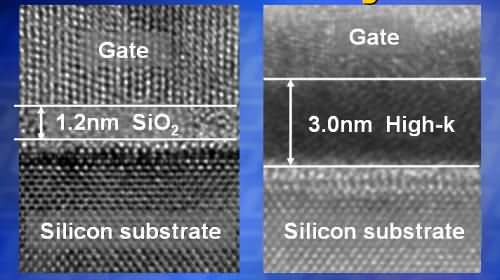

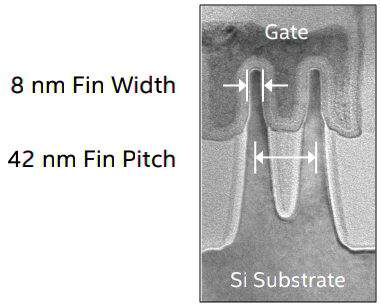

FinFET Transistors

The name from the English Fin - fin, crest. The technology was first used on 22 nm technology and is currently dominant in the production of processors. The bottom line is that not a complete layer of silicon on top of the oxide is epitaxially grown, but individual ridges in the zones cleared of oxide. UPD: a good link about FinFET from a5b , where initially a silicon wafer is etched to produce fins.

For example, like that. Source

Schematic comparison with planar technology - transistors become three-dimensional. A source

The shutter in this technology flows around the channel from three sides. When we apply voltage to the gate, it draws electrons (holes) from the depths to the tops of the ridges, and a channel is formed in them. Thus, the entire active zone of the drain, source, and gate goes into the ridges, and the leakage of currents deeper into the substrate is minimal. In this case, the ridge is not thermally isolated from the substrate and the heat freely leaves down.

Usually use two- or three-ribbed (three-gate) transistors. With such dimensions, making rectangular ridges as in the diagram is unrealistic, in shape it is rather a truncated cone.

Source

The same

Right below is our CMOS transistor. We see 6 ridges, 3 for the n-channel, 3 for the p-channel (indicated as Fin in the figure), and in the middle across the gate (Gate), along the edges there are contacts to the drain and source. The size of the transistor is determined by the distance between the ridges, the number of ridges, the channel width (all the same 25 nm or more), the size of the drain and source regions. The resolution of photolithography on the size of the transistor affects indirectly through the possibility of reducing the step between the ridges. For example, in 22 nm technology, the pitch between ridges is 54 nm, in 14 nm - 42 nm, in 10 nm - 34 nm. As you can see here, there is no linear dependence.

Now in the world there are only 3 companies that have mastered this technology. These are American Intel, Korean Samsung, and Taiwanese TSMC. Even AMD’s former daughter, GlobalFoundries, has dropped out of the process. AMD is currently ordering processors from TSMC and has entered into an agreement with Samsung.

A little bit about metallization

The metal tracks in the first, lowest layer of metallization have always been tried to be minimized. The fact is that the metallization path forms with the silicon the same flat metal-dielectric-silicon capacitor. But unlike the shutter, it is a stray capacitor. With a large capacitance at frequencies in gigahertz, spurious electrical communication may occur where it should not be. To reduce stray capacitance, you need to reduce the area of the tracks. Therefore, the tracks in the very first metallization layer are made as short and as thin as possible. For the same reason, they try to overlap different layers of metallization at a right angle - first make longitudinal tracks, the next layer transverse tracks. The higher the layer, the thicker the oxide beneath it and wider the track.

Why am I ?! Since the thickness of the first metal track is minimal, it is often indicated as the norm of the technological process. In FinFET technology, the space between the ridges is filled with oxide. A fairly thick layer on top of the High-k dielectric, gate, ridges and troughs. The first metallization layer is removed to these blockages above the troughs. The tracks themselves are made wider to reduce electrical resistance and compensate for bumps. Those. the smallest possible track width and reality also diverged.

Laminated Metallic Pie

Those. process standard is becoming more and more a virtual quantity. Therefore, we have similar processors with parameters marked by standards from 7 nm to 22 nm. FinFET 22 nm process allows you to get by with two ridges, 7 ridges need 3 ridges, as a result, the dimensions of the transistors are approximately the same. However, magazines often continue to write that with the transition from 10 nm to 7 nm, the number of transistors will increase 1.8 times. People still have old patterns from the Moore era ...

What next? The transition to volumetric transistors has led to the appearance of a large number of promising modifications. For example, Samsung announced GAAFET technology for 5nm technology.

Comparison of CMOS, FinFET and GAAFET is clear. A source

Those. the comb should not be continuous, but divided into separate threads. Question: Is the game worth the candle? - remains open. UPD: as F376 correctly noted , FinFet provides an input of an electric field from two parties. Gate-All-Around FET provides entry from all directions, which is more efficient.

There are also options for ring shutters, vertical, etc. There are combinations of FinFET and SOI. In general, the chemical processes of epitaxy are more complex, but more linear and predictable than lithography. It provides used for greater accuracy and the ability to create more subtle three-dimensional structure.

The situation on the modern market of microprocessor manufacturers and prospects

So, the three leaders stood out - Intel, Samsung and TSMC. Intel conducts under its own brands, the rest is mainly on order. Under the brands AMD, NVIDIA, Qualcomm, Apple, IBM are hiding chips manufactured at the TSMC or Samsung factories. Some old leaders fell off or ran into a barrier. The Chinese are trying to break into the big league, but so far not very successfully: they lack their own technological base, and world leaders in the production of equipment keep the latest technological lines for the Chinese.

The optimism of experts is associated with the transition to bulk structures and the beginning of the use of EUV lithography. Samsung and TSMC have begun to use it to a limited extent, for the most delicate structures. This gives them the opportunity to report on achieving standards of 7 nm and in the future up to 5 nm. Although, as already described, these numbers actually have little effect. The same Intel generally abandoned EUV. Apparently, they do not believe that this will greatly improve the performance.

On the other hand, people in the subject understand that the era of Moore's over, and each new step of productivity growth will require the used of lshih effort and time. The rapid growth of microelectronics ends ( sob! ). How did this happen once in the automotive industry and aviation. After explosive growth, slow development follows.

Among the promising breakthrough points, one can single out the transition to another material (not silicon) and the creation of multilayer microcircuits (3D integration - greetings to AMD's ideas). For 3D integration, you will have to drastically reduce heat generation or enhance heat dissipation.

That's all for transistor sizes. B of lshie reserves of productivity growth has in the other. In the optimization of architecture, for example. You can even make a marketing move, saying that a new processor with improved architecture works as if it were an old one with 0.5 nm technology. Therefore, we mark it as 0.5 nm. And figs with him that the dimensions of the transistors are the same.

It is possible to create new types of cells from combinations of transistors. For example, instead of 6 transistor memory cells, make 2 transistor structures with complex physics of mutual influence. Volumetric structures here provide many opportunities.

Physical limits

Someone may say that the author’s pessimism is not justified. They find ways to get around the restrictions. Maybe not as fast as before, but nonetheless.

The fact is that there are still physical processes that cannot be bypassed. The main ones are matter composed of atoms, and the charge carriers are electrons. To create a transistor smaller than an atom does not work. It will not work to create even less than 1000 atoms. Because there is an electron and Heisenberg's uncertainty relation. An electron is a very unstable particle, more or less stable behavior is possible only for an array of thousands and millions of electrons. On one electron, you can only destroy the Schrödinger cat.

Note: although there are developments on single-electron transistors ( 1 , 2 and 3)

Even at the current size, collisions occur due to spontaneous operation of transistors. If the probability of a collision is 10 -9 (one in a billion), then with the number of elements in billions and frequencies in GHz, this gives an average of 1 collision per cycle, or several billion collisions per second. To catch these, there are systems for monitoring the integrity of operations, and a suspicious operation is sent for re-execution.

With miniaturization, the number of collisions begins to increase very sharply. As a result, we come to a situation of zero or even negative effect from miniaturization. Those. transistors made less, they fit into the crystal more, but due to the growth of collisions and reprocessing cycles, the total productivity did not increase. Or maybe even fell. And this threshold is quite on the horizon.

A few words about domestic digital microelectronics

Contrary to popular belief, until 1985 the lag of the USSR from the leaders was not so big. About 3-4 years. This is if we take the leading enterprises in Zelenograd (note: BarsMonster wrote about Micron at the time ). Under Moore’s law, even a 3-4 year lag greatly affected performance. There were problems with obtaining high-quality oxide, with the clarity of pn junctions. If we add a conservative policy with the packaging of chips in the case (long contact lines did not increase the productivity of the devices), as well as the Soviet standards for the production of boards and cases with a bunch of iron (those who disassembled Soviet tape recorders will understand), we get a joke about the Soviet chip with cast-iron handles for carrying.

There are many reasons for the backlog. Later startanuli, limited resources, spraying resources. When the Americans focused on CMOS, ours continued to experiment with various technologies. They worked quite actively with silicon alternatives, primarily with A 3 B 5 materials . Well, the general relaxation of the late Soviet research institutes.

After 1985, the Americans started abruptly, and we started having problems. Then the 1990s, when life in the industry was warm by inertia. As a result, they entered the 21st century with 800 nm technology, when leaders had already stormed 130 nm. The second life of the industry was given by mass chipization of cards and government orders. The main production of steel: chips for SIM-cards, bank cards, payment cards, transport and discount cards and other consumer goods. Big gigahertz and small nanometers are not needed there.

Note: by the way, while in Moscow time there are one-time tickets (bought-used-threw-out, loaded up with a factory), in the same China they are actively promoting resource-saving technologies, in particular, the reusable use of the "token" on the subway (even for one short trip) .

Video about Shenzhen subway

Nevertheless, there is an attempt to enter the “big league” of microelectronics. Development goes in four main directions.

- «Суверенные» техпроцессы. Попытка создать полный цикл производства на аппаратуре отечественного производства и собственными техпроцессами. Идем тем же путем, который прошли лидеры лет 20 назад, но с учетом найденных граблей и путей решения. Из последнего что было в открытых источниках это 250 нм в серии и 150 нм в процессе внедрения. Сюда же можно отнести попытку создать собственные установки EUV-литографии на 13,5 нм и таким образом сразу выйти если не в высшую лигу, то вплотную к ним.

- Закупка технологических линий у ведущих мировых производителей. Проблема тут в том, что самые современные установки нам не продавали даже в лучшие годы. Обычно продают устаревшие линии, которые сняли с производства. Сейчас в связи с санкциями тем более. Тут можно вспомнить эпопею с закупкой «Ангстремом» оборудования дрезденского завода AMD в 2007, под техпроцесс 180 нм. Или закупку «Микроном» 90 нм линии у французской STMicroelectronics с последующим апгрейдом до 65 нм. Пока это самый тонкий техпроцесс в России, успели урвать перед санкциями. Правда есть сейчас и обходной путь – закупка через Китай.

- Заказ производства на заводах в Китае или Тайване. При этом архитектура и топология полностью разрабатываются у нас,

сейчас даже делаются собственные фотошаблоны. Китайцам остается только воспроизвести техпроцессы на своих заводах. Получаем более совершенные производительные процессоры, и развиваем компетенцию в области разработки самых современных процессорных систем. Здесь задействованы уже не группа ученых-Кулибиных, а большие конструкторские коллективы. Из полного цикла выбывает только последний участок – производство.

Прим.: Байкал сделан как раз по нормам 28 нм на фабрике TSMC. Статья о выходе Байкала и его разбор. - Развитие альтернативных технологий. Это разработка перспективных технологий, которые могут стать массовыми в будущем. Сюда входят работы по соединениям A3B5 и гетероструктурам, прежде всего арсениду и нитриду галлия. А также попытки оптимизировать электронно-лучевую и рентгеновскую литографию для массового производства, что вообще снимает ограничения литографии.

Прим.: сильная школа по гетероструктурам нам досталась от ныне покойного Алфёрова, но даже с господдержкой OptoGaN не вытянул, рынок и конъюнктура подводят.

In general, the situation is not brilliant for Russian microelectronics. But there is hope that the leaders will inevitably slow down due to physical limitations, and here we, slowly hurrying, creep up behind.

The final chord about memory and windows of opportunity in the third part in a couple of days - stay tuned!

Do not forget to subscribe to the blog : it’s not difficult for you - I am pleased!

And yes, please write about the shortcomings noted in the text in the PM.