FPGA is simple or do-it-yourself alu

On Habré there are a lot of articles devoted to microcontrollers and programming languages on them, but articles about FPGA programming are not often found. Firmware for FPGAs can be written in hardware description languages or draw diagrams in CAD systems of firms manufacturing FPGAs. Today I want to show how it is possible to program ALU on the FPGA of Actel A3P250 (ProASIC 3 with the number of equivalent gates 250 000) in the language of the SystemVerilog hardware description. This FPGA is interesting in that it allows you to prototype custom ASIC or BMK chips. The firmware that is synthesized for this FPGA can be converted with a serial chip.

Who cares, welcome under the cat.

So, the creation of firmware can be divided into several stages:

1. We determine what we want to get, draw on a piece of paper, in the head or in Visio, a structural diagram of the future device. In my case, it is ALU, it has inputs: two operands of 4 bits each, a reset input, a synchronization input, an operation code input of 2 bits (00 - addition, 01 - subtraction, 10 - multiplication, 11 - the result is 0) and exit with the result of 8 digits.

2. If the project is complex, then you need to write a behavioral model, in some high-level language such as C #, by which you can understand how it will work, in this case I will skip this item, because I’ll write in C or C # model This device will be able to many, and I'm sure better than me.

3. Actually write the code, for this I use NPP with syntax highlighting SystemVerilog although you can write in any text editor or in one of the programs for modeling, synthesizing or tracing the microcircuit, but more on that later.

The firmware code at this stage I will call the logical model, although it may be different in different sources.

4. We are writing a test for our logical model; several methods can be used for this. Also at this stage we combine the test and the model.

5. Run our model with a test in a simulation environment. I use QuestaSim for modeling, this is an advanced version of ModelSim from Mentor Graphics.

6. If the tests are successful, then you can proceed to the synthesis. For synthesis, I use Precision Synthesis from Mentor Graphics. But you can use the software that provides you the manufacturer of the chip. As a result of the synthesis, we get files in the * .edf and Verilog format, this is a logical model assembled by CAD synthesis from the blocks that are in the FPGA, as well as a description of the relationships between them. I will call these files net-sheets.

7. No-sheet file in Verilog format must be connected instead of the logical model and re-run the simulation to make sure that the synthesis is successful and the synthesizer does not throw anything superfluous, it knows how to do this. Also at this stage, you can use the means of formal verification, which will check the conformity of the received net-list of the logical model.

8. If the netlist has passed the test, you can start placing and tracing the netlist in the FPGA, for this I will use the Actel Designer, which is part of the Actel Libero IDE. At this stage, we get the finished FPGA firmware and, just as importantly, the revised net-list and time delays in its circuits, the net-list is again in Verilog format, and the delays are generated in * .sdf format.

9. Now you need to simulate the net-list obtained as a result of tracing with time delays and make sure that everything works.

10. If everything really works, then you can flash it.

Now back to ALU.

The code in SystemVerilog consists of modules, at least in the part regarding the hardware description, because when testing, the class and program keywords appear.

It is not sad, but there is no tag for SystemVerilog, or at least Verilog, but there is a tag for VHDL, I had to use it ...

Let's analyze the ALU module in parts.

First, we announce the name of the module and the inputs / outputs, remember we defined them in the first stage.

Then we declare several internal lines for connecting the combinational part and the trigger part.

Now we describe the combination or asynchronous often ALU:

And finally, the trigger or synchronous part of the ALU, because the ALU will be synchronous with us

We close the module with the keyword:

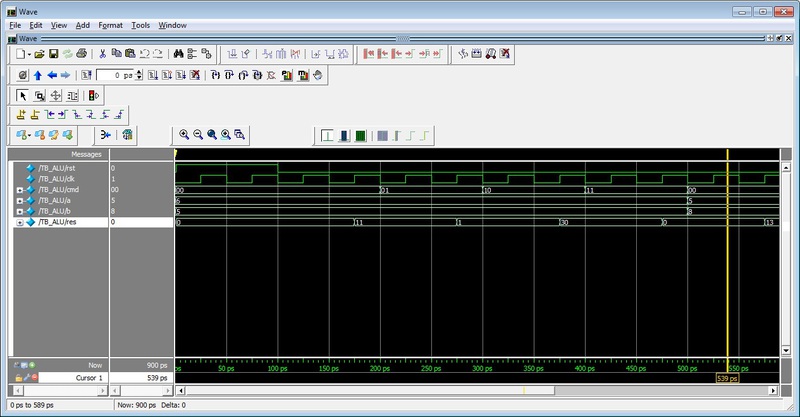

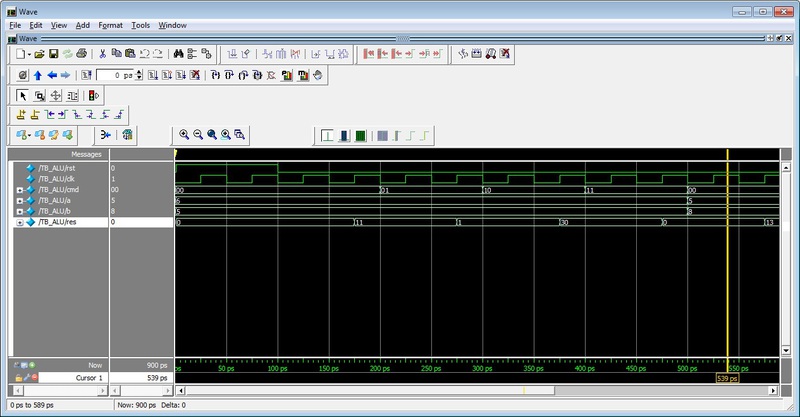

Now we will write a test and run the simulation, we will get the following time diagram:

As we see the operations are performed, but due to two triggers at the input and the output there is a delay of 2 cycles, this can be fixed, but we just look at the example, and not create Core i7, so let’s leave it and proceed to the synthesis: The

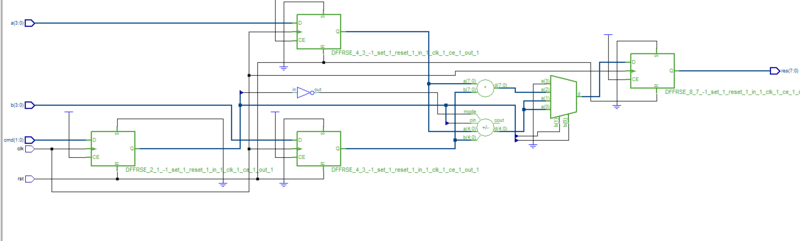

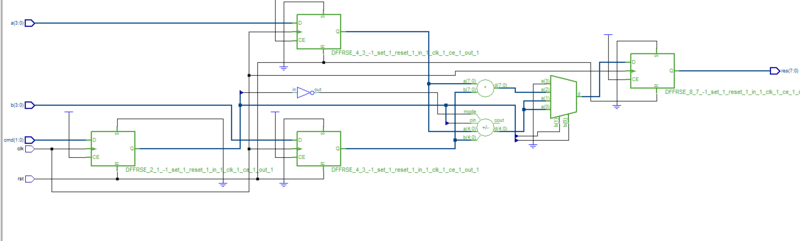

synthesizer decided that our circuit will look like the one in the figure above, in fact, I agree with him, although this is not always the case and therefore I won’t even start the test once again. to trace to the crystal.

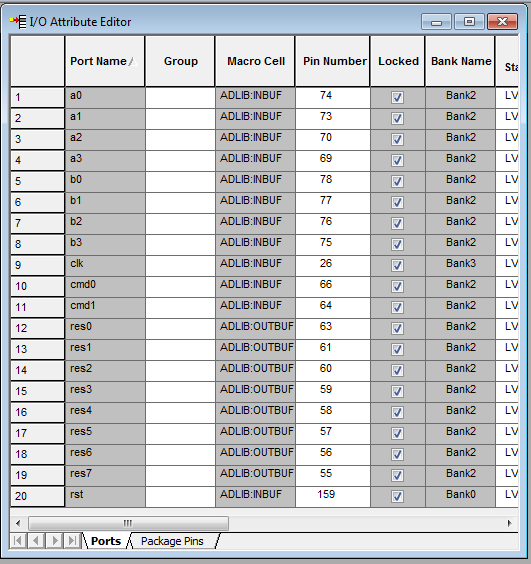

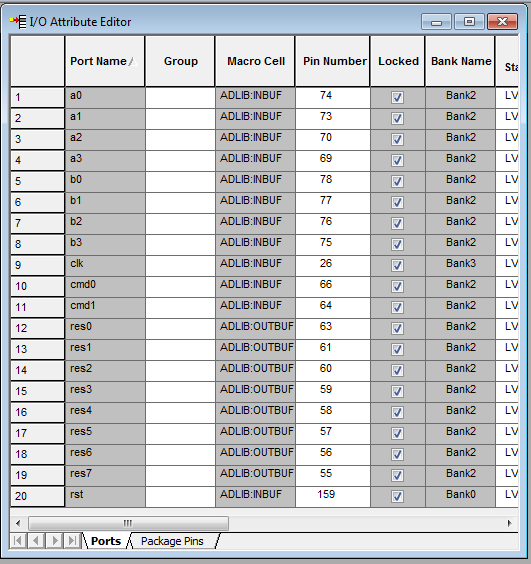

Because I have a kit design, I will arrange the FPGA conclusions as follows:

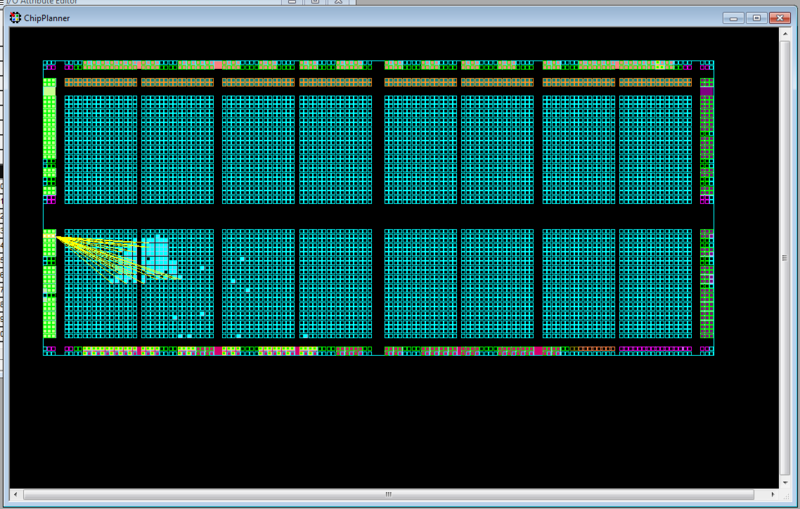

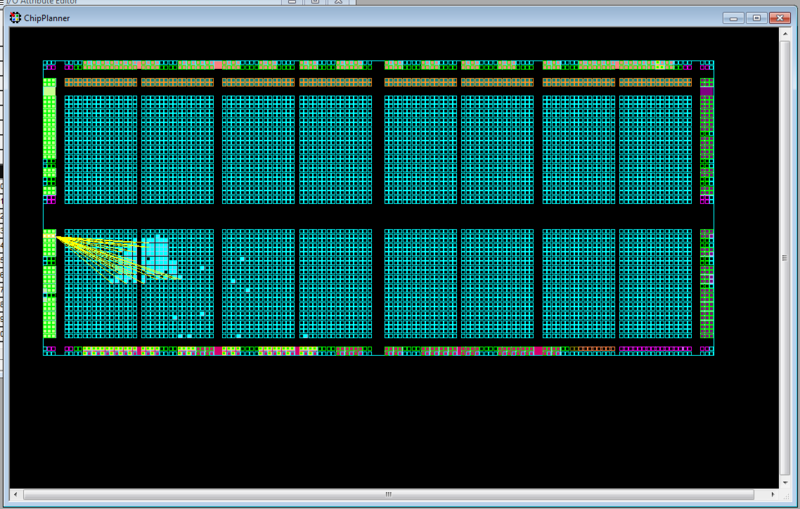

The result of the tracer (placing elements in the crystal) in the figure below, by the way, at this stage, you can move the elements around the crystal.

Yellow indicates the clock circuit.

On this I want to end my story, the video will be later.

Thanks to everyone who read to the end, I apologize for the style and possible errors in the text, but I'm not a writer, I'm just learning.

PS Who has been interested in FPGAs for 3 years now, this ALU project was completed in an hour, a simple layout was needed to test one technique for making failures.

Who cares, welcome under the cat.

So, the creation of firmware can be divided into several stages:

1. We determine what we want to get, draw on a piece of paper, in the head or in Visio, a structural diagram of the future device. In my case, it is ALU, it has inputs: two operands of 4 bits each, a reset input, a synchronization input, an operation code input of 2 bits (00 - addition, 01 - subtraction, 10 - multiplication, 11 - the result is 0) and exit with the result of 8 digits.

2. If the project is complex, then you need to write a behavioral model, in some high-level language such as C #, by which you can understand how it will work, in this case I will skip this item, because I’ll write in C or C # model This device will be able to many, and I'm sure better than me.

3. Actually write the code, for this I use NPP with syntax highlighting SystemVerilog although you can write in any text editor or in one of the programs for modeling, synthesizing or tracing the microcircuit, but more on that later.

The firmware code at this stage I will call the logical model, although it may be different in different sources.

4. We are writing a test for our logical model; several methods can be used for this. Also at this stage we combine the test and the model.

5. Run our model with a test in a simulation environment. I use QuestaSim for modeling, this is an advanced version of ModelSim from Mentor Graphics.

6. If the tests are successful, then you can proceed to the synthesis. For synthesis, I use Precision Synthesis from Mentor Graphics. But you can use the software that provides you the manufacturer of the chip. As a result of the synthesis, we get files in the * .edf and Verilog format, this is a logical model assembled by CAD synthesis from the blocks that are in the FPGA, as well as a description of the relationships between them. I will call these files net-sheets.

7. No-sheet file in Verilog format must be connected instead of the logical model and re-run the simulation to make sure that the synthesis is successful and the synthesizer does not throw anything superfluous, it knows how to do this. Also at this stage, you can use the means of formal verification, which will check the conformity of the received net-list of the logical model.

8. If the netlist has passed the test, you can start placing and tracing the netlist in the FPGA, for this I will use the Actel Designer, which is part of the Actel Libero IDE. At this stage, we get the finished FPGA firmware and, just as importantly, the revised net-list and time delays in its circuits, the net-list is again in Verilog format, and the delays are generated in * .sdf format.

9. Now you need to simulate the net-list obtained as a result of tracing with time delays and make sure that everything works.

10. If everything really works, then you can flash it.

Now back to ALU.

The code in SystemVerilog consists of modules, at least in the part regarding the hardware description, because when testing, the class and program keywords appear.

It is not sad, but there is no tag for SystemVerilog, or at least Verilog, but there is a tag for VHDL, I had to use it ...

Let's analyze the ALU module in parts.

First, we announce the name of the module and the inputs / outputs, remember we defined them in the first stage.

module ALU

(

input rst, clk, // Сброс и синхронизация

input [1:0] cmd, //Командное слово

input [3:0] a,b, //Операнды

output logic [7:0] res //Результат

);

Then we declare several internal lines for connecting the combinational part and the trigger part.

logic [3:0] A, B;

logic [1:0] Cmd;

logic [7:0] outpRes;

Now we describe the combination or asynchronous often ALU:

always_comb

begin

unique case(Cmd)

2'b00:

begin:add

outpRes = A+B;

end:add

2'b01:

begin:sub

outpRes = A-B;

end:sub

2'b10:

begin:mul

outpRes = A*B;

end:mul

2'b11:

begin:div

outpRes = 0;

end:div

endcase

endAnd finally, the trigger or synchronous part of the ALU, because the ALU will be synchronous with us

always_ff @(posedge clk, posedge rst)

if (rst)

begin

res <= '0;

A <='0;

B <='0;

Cmd <='0;

endelsebegin

A[3:0] <= a;

B[3:0] <= b;

Cmd <=cmd;

res <= outpRes;

endWe close the module with the keyword:

endmodule

Now we will write a test and run the simulation, we will get the following time diagram:

As we see the operations are performed, but due to two triggers at the input and the output there is a delay of 2 cycles, this can be fixed, but we just look at the example, and not create Core i7, so let’s leave it and proceed to the synthesis: The

synthesizer decided that our circuit will look like the one in the figure above, in fact, I agree with him, although this is not always the case and therefore I won’t even start the test once again. to trace to the crystal.

Because I have a kit design, I will arrange the FPGA conclusions as follows:

The result of the tracer (placing elements in the crystal) in the figure below, by the way, at this stage, you can move the elements around the crystal.

Yellow indicates the clock circuit.

On this I want to end my story, the video will be later.

Thanks to everyone who read to the end, I apologize for the style and possible errors in the text, but I'm not a writer, I'm just learning.

PS Who has been interested in FPGAs for 3 years now, this ALU project was completed in an hour, a simple layout was needed to test one technique for making failures.