RAM Expansion Board for Apple IIgs

- Transfer

- Tutorial

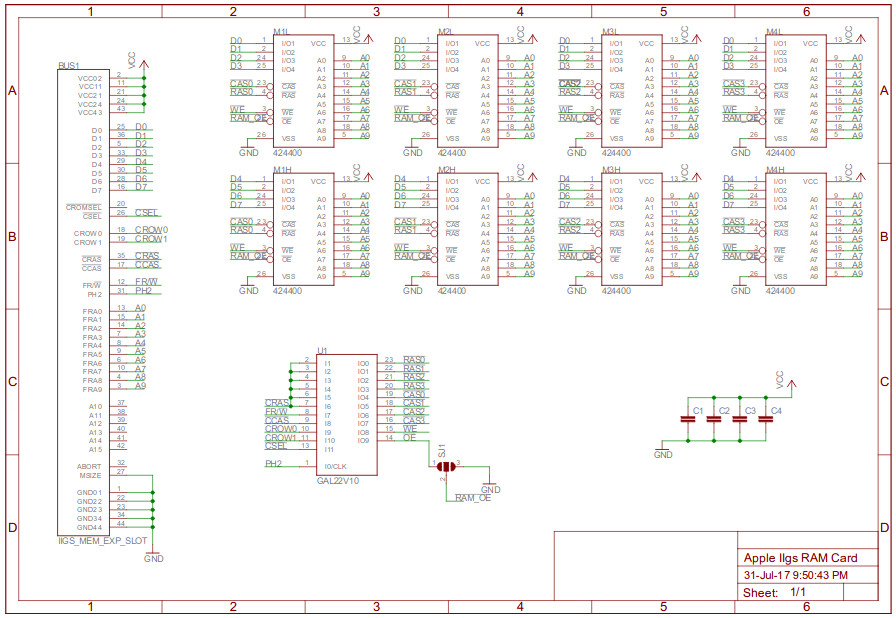

The proposed RAM expansion board for the Apple IIgs computer is based on NEC uPD424400-70 chips from several 1-megabyte SIMM modules. Each of these microchips stores 1 M nibbles and is housed in a 26-pin SOJ type case.

The Apple IIgs computer is powered by a 65C816 processor - 16-bit, but with an 8-bit data bus. The expansion card contains 4 MB of RAM. The memory is divided into four lines, 1 MB each. The line consists of two chips of 1 M nibbles, so a total of eight chips were required.

The computer already has a slot for the RAM expansion card. It displays all the necessary signals, the computer also takes care of the regeneration of dynamic RAM. Therefore, the expansion card is quite simple. The author decided to make the board small-sized, since the cost of its manufacture depends on this, and also put all the logic in the GAL22V10 FPGA.

The following signals are present on the RAM expansion slot:

FRA0-FRA9 - 10-bit multiplexed cell address, fed directly to the address inputs of the dynamic RAM chips

CROW0, 1 - two bits to select one of the four lines

/ CRAS - gate address signal of the dynamic RAM

/ CCAS - signal gating column address of dynamic RAM

FR / W - permission to write to RAM, this signal requires additional processing, see below

D0-D7 - data bus, connected directly to the input / output lines of RAM

/ CSEL chips - a logical unit appears on this line when reading from RAM, it must be invert and apply to the inputs / OE of the microcircuit RAM

MSIZE - tells the computer the volume of the line: one - 256 kB, zero - 1 MB, here this line is connected to a common wire

14M, PH2CLK, A10-A15 - the proposed board does not involve

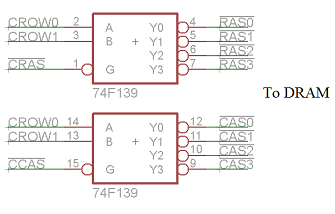

signals / CRAS and / CCAS needs to be demultiplexed to receive separate / RAS and / CAS signals for I am each of the lines. For this, the 74F139 chip is suitable (hereinafter it is understood that there will be no separate chips on the board, instead of them there will be one common FPGA).

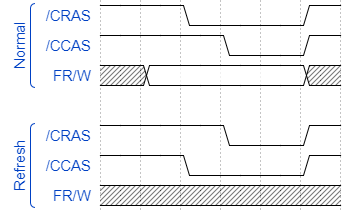

The FR / W signal cannot be fed directly to the / WE input of the dynamic RAM chips, and this is why. In a normal read-write operation, the / RAS line first becomes active (which corresponds to a logical zero), then the / CAS line. During a dynamic RAM regeneration cycle, on the contrary, the / CAS line becomes active first, then / RAS becomes active. But the chips used require that a unit appears on the / WE line before the / RAS line becomes active. And the FR / W signal coming from Apple IIgs does not meet this requirement. The state of FR / W during the regeneration cycle is undefined. Therefore, a circuit is required that detects a regeneration cycle and feeds a unit to / WE.

The first step is to identify the regeneration cycle. Below is the timing chart:

The author’s idea is to use a “transparent” latch. The / CRAS signal for it is the input signal, / CCAS is the latch signal. When the unit is on / CCAS, the device passes the input signal through itself: the state of the output changes after the state of the input. When / CCAS goes from one to zero, the latch remembers the signal at the input, and now it does not change at the output. In a normal read / write operation on / CRAS, zero is present at the time of switching / CCAS from one to zero. And during the regeneration cycle on / CRAS, there is one also at the moment of switching / CCAS to zero. Then, when / CCAS switches back to one, the latch becomes transparent again. It reminds a fantastic flower from “Secrets of the Third Planet”, which can be both a “mirror” and a “camera”.

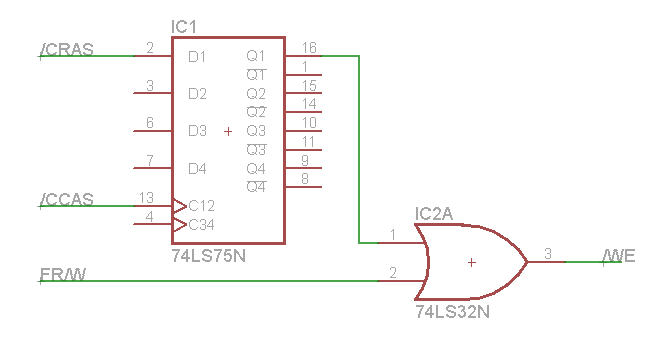

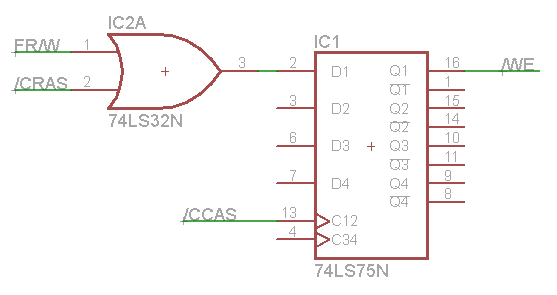

At first, the author drew up the following scheme:

But for its transfer to the GAL22V10 FPGA, two output pins are required. Therefore, the scheme had to be simplified. During normal operation, the FR / W signal takes the desired value until it clicks, so this is also possible.

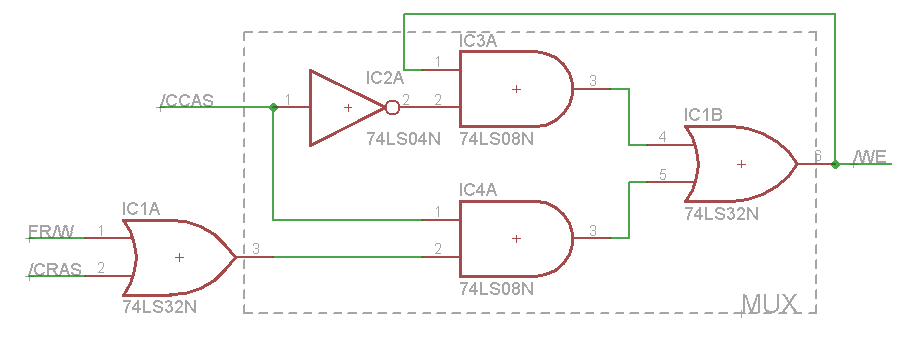

A “transparent” latch can be made from a multiplexer, and it, in turn, from logic elements. The scheme becomes this:

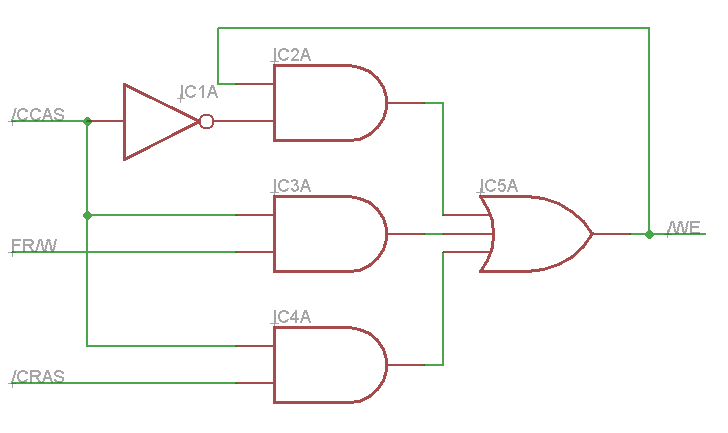

And after simplification - this:

This option is transferred to the FPGA. For compilation, the author used WinCUPL. This program is on the Atmel website. It is raw and constantly flies, but it coped with the task perfectly. Programmer - Genius G540.

Jumper SJ1 on the board acts like this. If pins 1 and 2 are connected, the / OE signal passes through the FPGA. If pins 2 and 3 are connected, it is connected to a common wire. The author was not sure that the scheme for identifying the regeneration cycle would work. Therefore, he added this jumper in case the FPGA configuration had to be redone.

Since it turned out that everything works, you do not need to solder the pins, just connect the terminals 1 and 2 with a drop of solder.

To reduce the size of the board, the author applied one power capacitor for every four RAM chips, and placed the chips themselves on both sides of the board.

Microchips in SOJ cases are difficult to solder, and especially soldering, with a soldering iron. The author recommends using a hairdryer.

Expand the chips correctly. On the bottom line they are inverted. Pin 1 looks down.

Some through holes are too close to the pads. Do not short circuit them with solder.

And platforms 1 and 2 for the jumper, on the contrary, close.

Capacitors C1 - C3 have a capacitance of 0.1 μF, C4 - 10 μF.

The author ordered the boards at OSH Park. The ENIG coating is applied - gold, but very thin. For game cartridges is not suitable - it will quickly be erased. And here the board was placed in the slot once and more is not removed from there.

The author thanks GGLabs for the circuit of a similar board, it helped a lot, thanks!

The finished circuit turned out like this:

Files:

Firmware FPGA GAL22V10 , the program WinCUPL version 5.30.4 is applied

Board , applied program Eagle version 7.1

Scheme in PDF

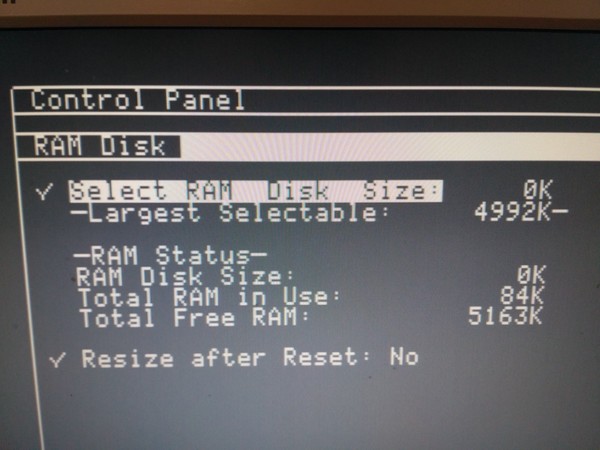

Earned!