T1 - discrete 8-bit DIY computer

There were always a lot of “homemade” ones. With the advent of the network, lovers of doing something with their own hands immediately organized themselves, and created a lot of different kinds of communities, forums and other places where you can chat with your own kind. Thanks to this, interesting works regularly appear on the Internet, some of which are worth paying close attention to.

One of such works is, in particular, a project to create a discrete 8-bit computer. The author of the project is Andrew Starr , and the project itself is located here on this page . What is a project like?

According to the author, this is partly kinetic assembly, partly a tribute to the achievements of science and technology, and the achievements of past years. In part, this is an educational project.

To create this system, the author uses the following elements:

- 8-bit bus

- 2 * 64 bit stacks (data, return);

- Harvard architecture : 256 byte main memory and 256-word program memory;

- 13-bit software command word: 5 bits per opcode, 8 bits operand;

- All memory elements are made using ferrite cores;

- Program memory is made using ferrite transformers;

- Logic elements are made of discrete elements in the form of plug-in modules;

- The target clock frequency is 1 MHz.

In Harvard architecture, the characteristics of memory devices for instructions and memory for data need not be the same. In particular, word width, clocking, implementation technology, and memory address structure may vary. On some systems, instructions may be stored in read-only memory, while data storage typically requires read and write memory. Some systems require significantly more memory for instructions than memory for data, since data can usually be loaded from external or slower memory. Such a need increases the bit width (width) of the instruction memory address bus in comparison with the data memory address bus.

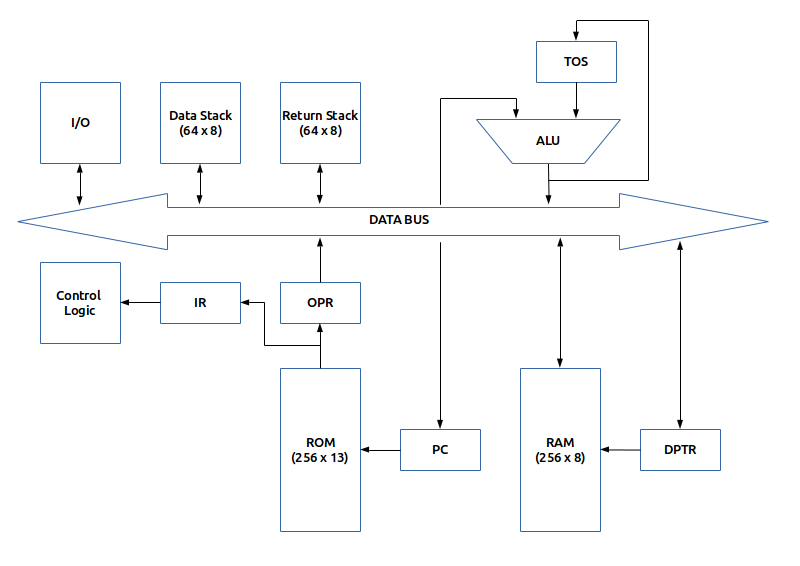

System Architecture:

It uses a standard 2-stack machine with several modifications that allow using the Harvard architecture and the optional data field in the instructions.

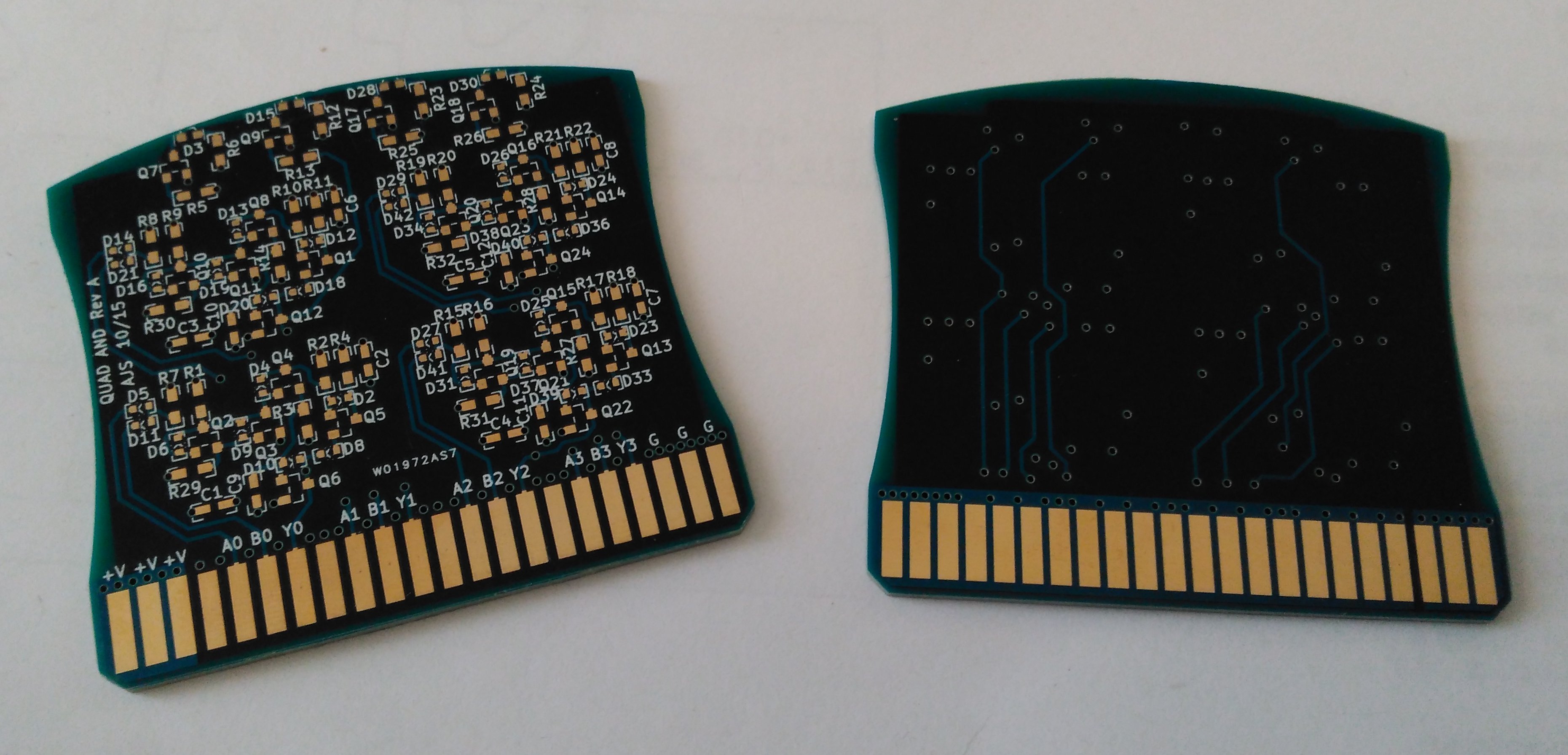

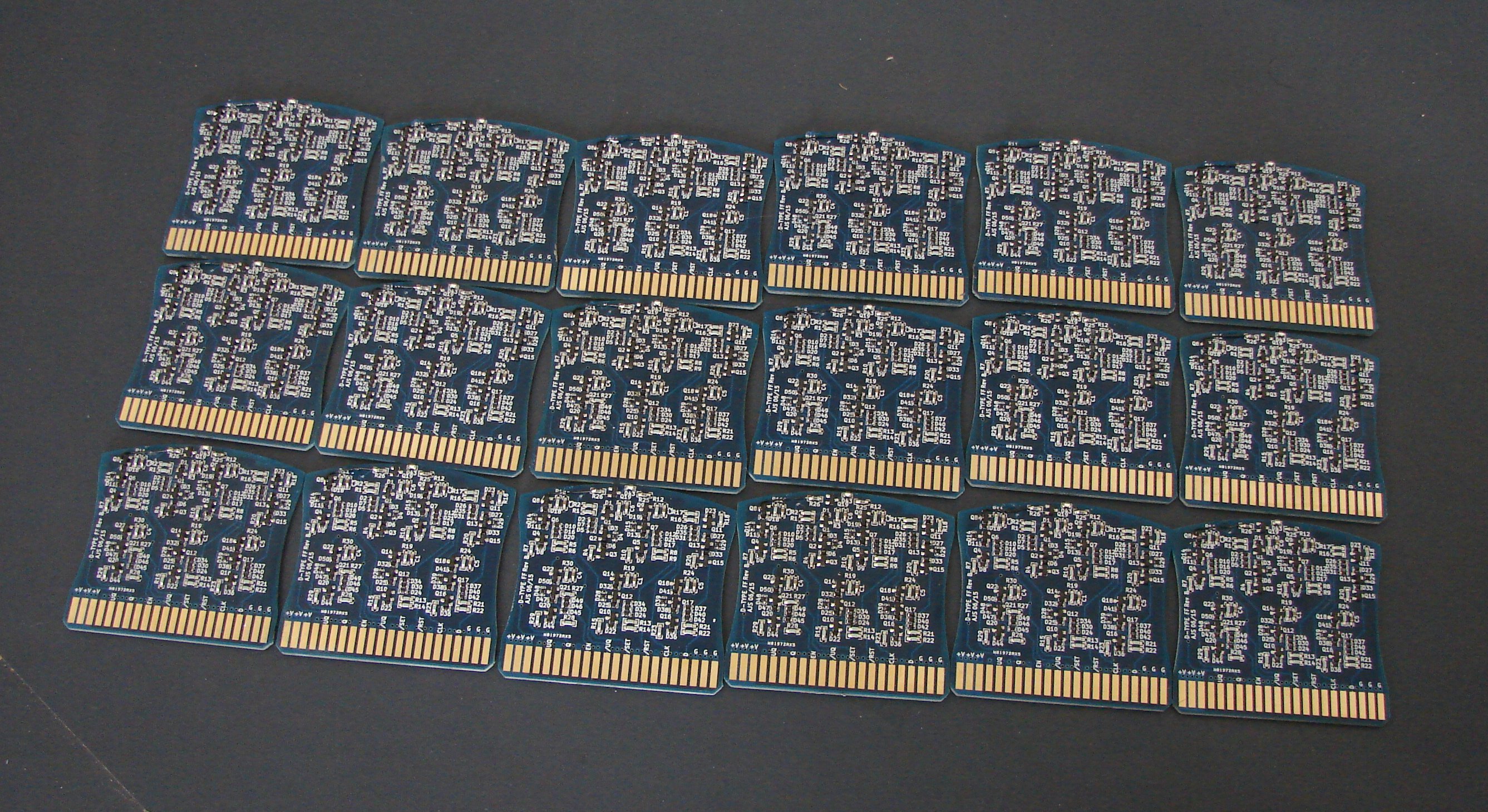

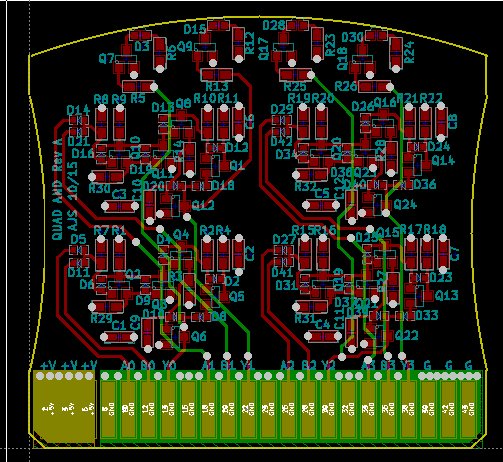

Now the author has already developed an AND-module scheme, and ordered the appropriate modules, which arrived the other day.

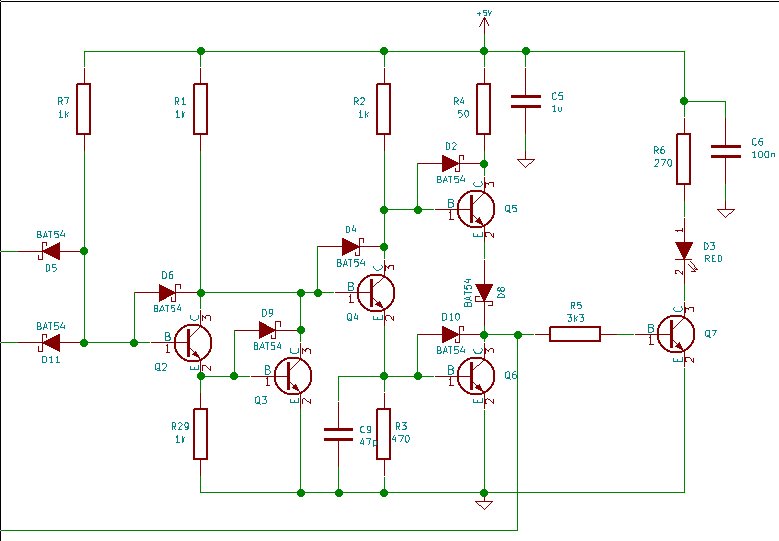

Schemes

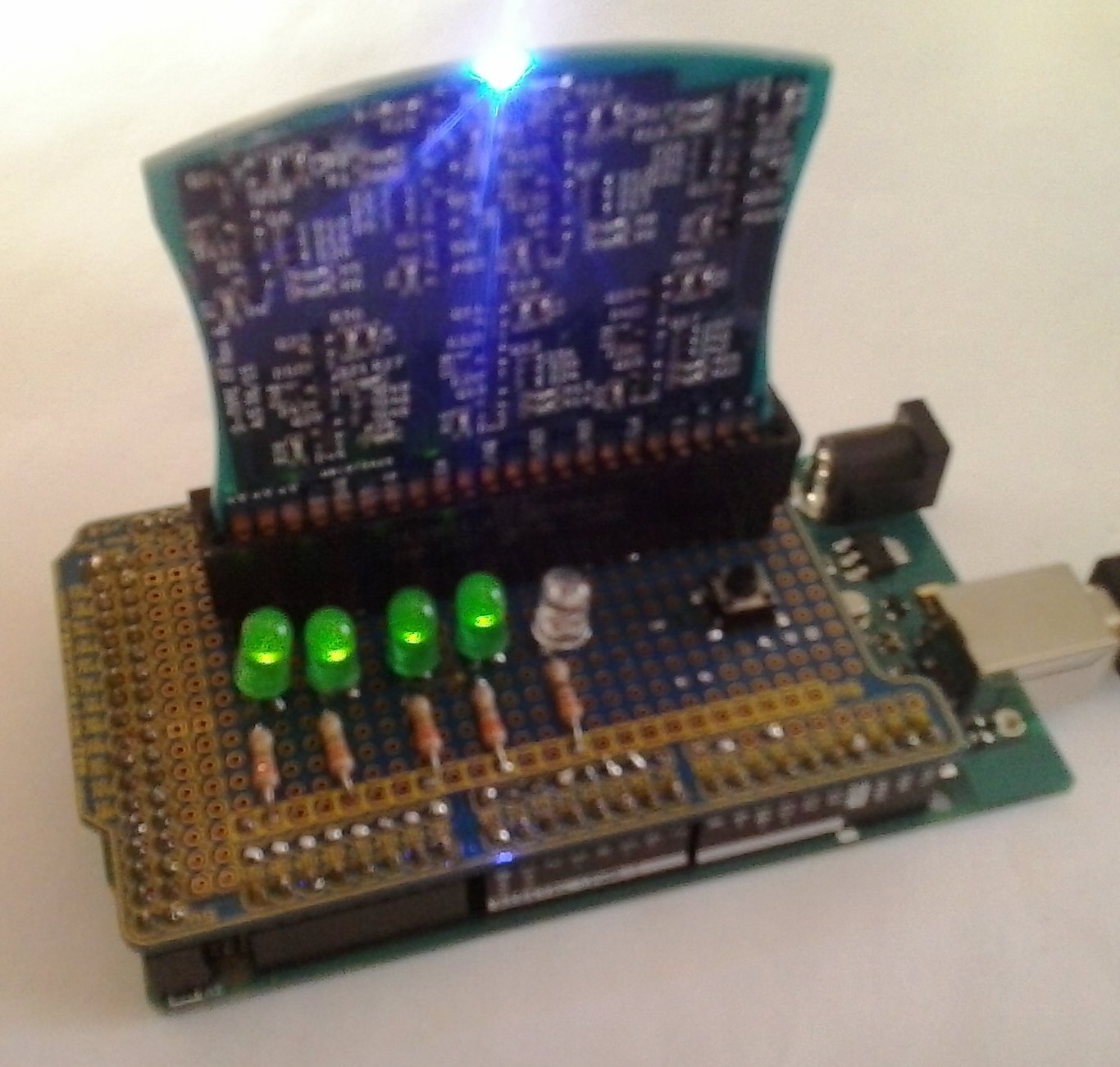

Testing:

Other components are also ready, including address decoders for stack memory.

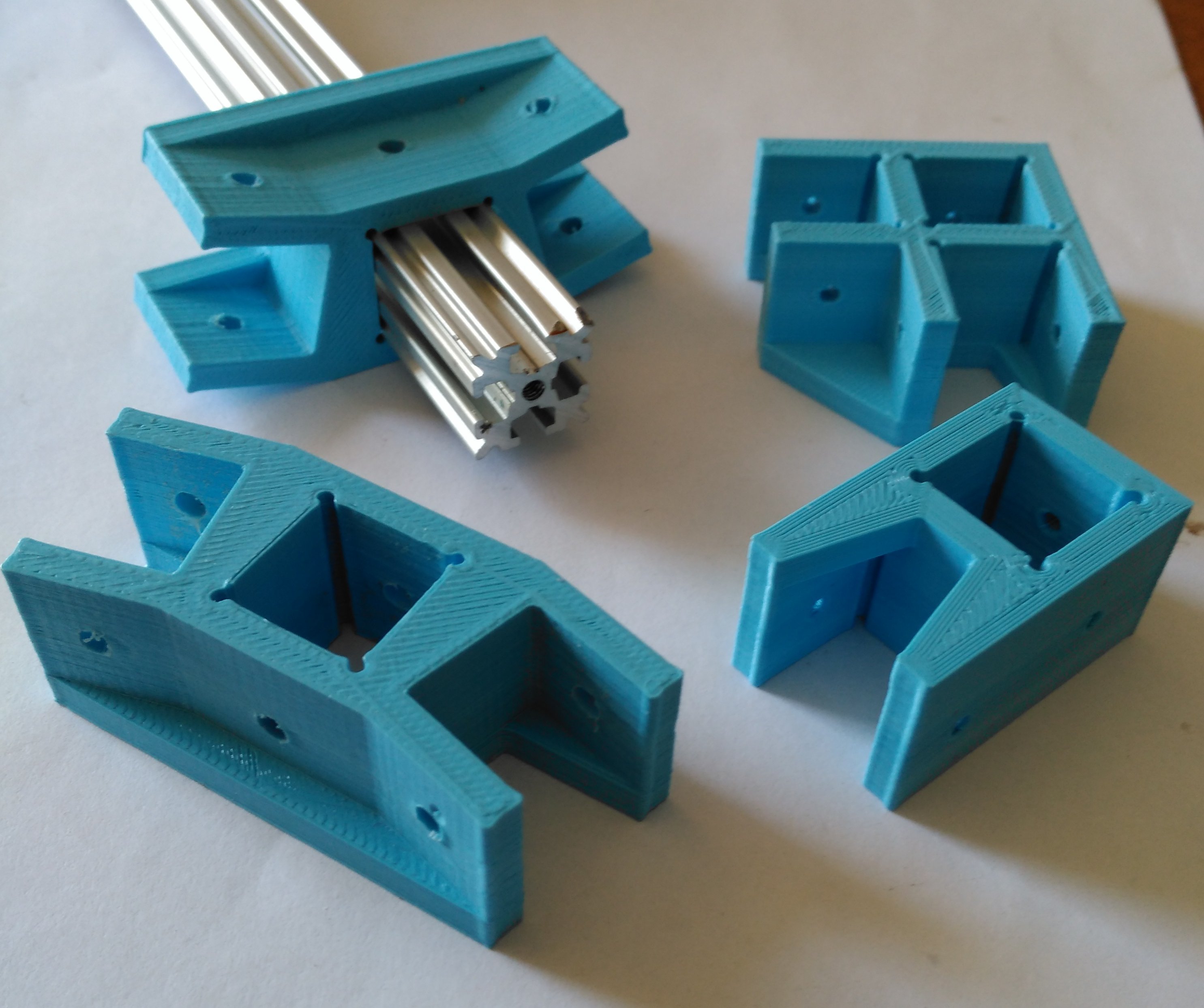

Among other things, the author is also developing a case for his creation:

Now the work is still ongoing, so you can monitor the implementation of the project here .