Connecting the ADC to the FPGA. Features, difficulties, implementation

Hello! This article will discuss the connection of ADC chips to FPGA crystals. The main features of connecting circuit nodes will be considered, modern ADCs and their characteristics will be presented. The article will give practical tips on how to quickly and correctly connect the ADC to the FPGA with minimal time costs. In addition, we will talk about the principles of connecting one or another ADC, we will consider the input FPGA buffer and its basic components - triggers, delay nodes IODELAY, ISERDES serializers, etc. In more detail, with examples of program code in VHDL, an overview of the basic elements required for high-quality reception of data from the ADC will be carried out. This is an input buffer, a data packing node for single-channel and multi-channel systems, a FIFO-based data synchronization and data transmission module, an ADC programming node using the SPI interface, data frequency synthesis node - MMCM / PLL. Also, the article will provide an overview of finished devices (in the FMC standard) from leading foreign and domestic manufacturers of analog and digital circuits. At the end of the article you will find a link to the source codes of the universal node of the receiver of data from multi-channel ADC circuits. The code is simple and flexible in configuration; it is presented in the VHDL language and is sharpened on FPGAs of Xilinx 7 series and higher, but can also be used in other FPGA crystals.

Article outline

- ADC (general overview, purpose, element base)

- Examples of completed ADC modules of various manufacturers

- Connecting the ADC to the FPGA. FPGA selection. Number of contacts, logical resources, data transfer interface

- FPGA input buffer. Composition, main components. Appointment

- Data packer for single-channel and multi-channel schemes

- Data Sync Node (FIFO)

- ADC control via SPI interface (example)

- Inner tire. Connecting FPGAs to a remote device

- ADC data receiver source codes

- List of references

A / D Converters

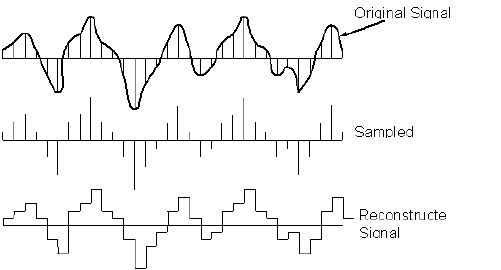

ADCs are used for a wide class of radio engineering tasks - in any devices where it is required to convert an analog signal to digital form. They can be used in audio and video systems, used in problems of hydroacoustics and hydrocommunications (low sampling frequency, high bit depth), in devices for converting the radio frequency range (DDC / DUC circuits), in radar and radio navigation (high sampling frequencies, medium bit data). ADCs are used in digital voltmeters and multimeters, in computer video input boards, video cameras, speech recognition systems and sound devices. Fast ADCs are used in oscilloscopes and spectrum analyzers, and are used in laboratory equipment and medical equipment. Very often, the ADC is used in the tasks of collecting and processing data at high speeds.

As you can see, ADC chips are an integral part of analog-to-digital devices. In the modern world it is very difficult to find a device in which there would be no ADC. The classic look of the ADC is shown in the following figure.

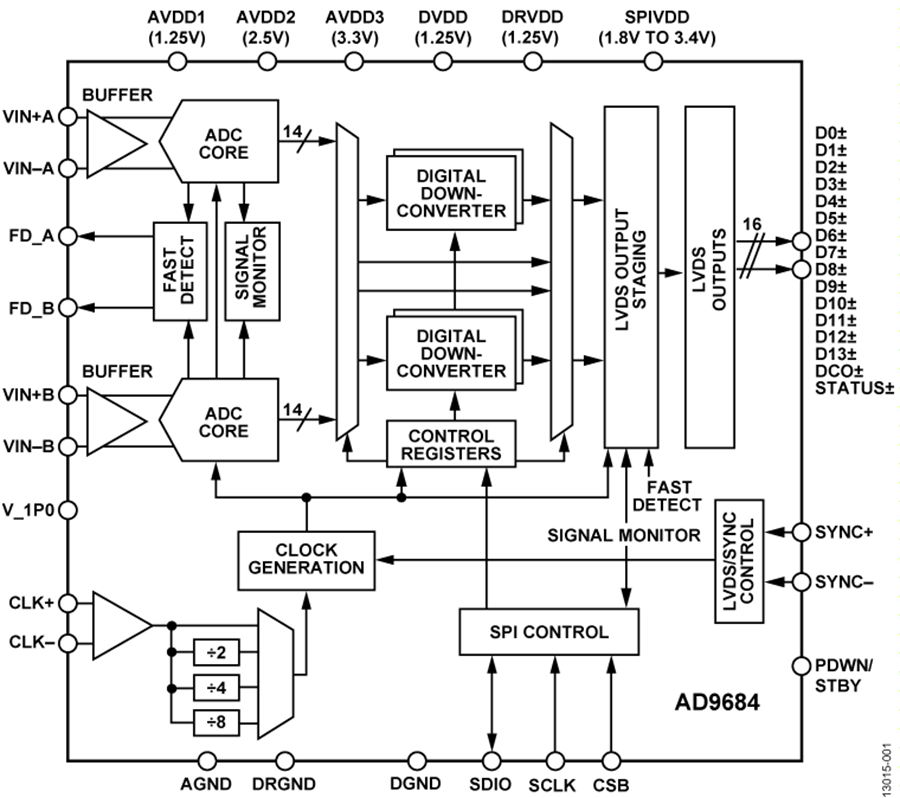

This is a simplified diagram taken from a datasheet on an AD9684 chip. It contains two differential analog inputs VINA and VINB , CLK clock input , SPI control, parallel output bus D0-D13 , voltage points of various components of the microcircuit, synchronization block SYNC and other control signals.

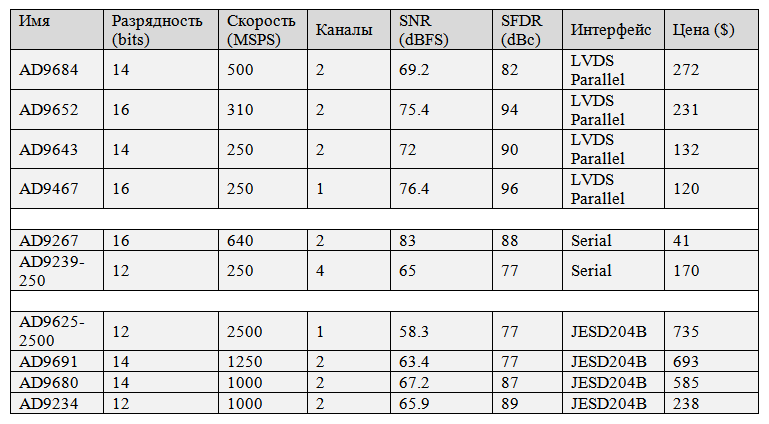

It is obvious that ADC microcircuits are characterized by a set of certain parameters that determine the final choice of the user and which determines the scope of the ADC. By digital part- This is the data transfer rate (effective clock frequency), which can range from several tens of kHz to several GHz. The capacity of the data at the output of the ADC is in modern devices from 8 to 32 bits of data. On the analog side , these are the signal-to-noise ratio ( SNR ) and the spurious-free dynamic range ( SFDR ), usually expressed in decibels (typical SNR levels range between 70-80 dB and SFDR levels around 90 dBc). Important parameters when choosing an ADC are the dissipated power (W), the number of channels in one housing, the interface with a digital node, and, of course, the cost of the component.

Consider modern high-speed ADCs and their characteristics using the example of a table taken from the well-known site Analog Devices, a giant in the production of all kinds of ADC and DAC chips. For convenience, the table summarizes the most important characteristics of microcircuits, they are divided by the type of communication interface with a digital device and arranged according to the speed of information transfer (clock frequency) from a larger value to a smaller one.

The table presents 4 top-end microcircuits that transmit data in parallel form according to the LVDS standard. The bit depth of data is 14-16, channels 1-2, the maximum sampling frequency is 500 MHz. The average SNR and SFDR are 70 dBFS and 90 dBc, respectively. For some circuits with a serial data bus (Serial), the characteristics are almost similar. For modern ADC chips that use the JESD204B transmission interface and connect to the FPGA via gigabit lines, the clock frequencies are much higher, but the analog characteristics are slightly worse (at least due to the fact that the digital data capacity is lower - 12 and 14 bits). This article will notConsider connecting an ADC to FPGA crystals through gigabit lines. I will focus on a simple and well-studied option for connecting microcircuits - a serial and parallel bus with data transfer interfaces such as LVTTL, LVDS, LVCMOS, LVPECL . In particular, an interesting way to transfer data on the LVDS bus, which is distinguished by the simplicity of PCB tracing, low cost performance, low noise and power dissipation, as well as high data transfer speed. FPGAs use serializers / deserializers to receive serial bus data. For a parallel bus, everything is much simpler and the data is accepted as is.

In the course of work on pairing analog and digital devices, I had to master the following ADC chips. These are already obsolete but still used -AD9224, AD6644ST-65, AD9244, LCT2207, ADS5474, AD9432BST-105, AD7475BR , modern level microcircuits - AD9430BSV, ADS54RF, AD9467, ADC12D1800, AD9680 and others. Since my area of work is only partially related to analog circuitry, I’m unlikely to tell you about ways to improve the performance of finished analog-to-digital modules. Also, I will not be able to give advice on the qualitative construction of analog paths and the methodology for choosing one or another circuit component to achieve the best analog performance (SNR, SFDR). But I will try to answer the questions of connecting the ADC to FPGA crystals and further data processing within the framework of this article.

Examples of ADC modules

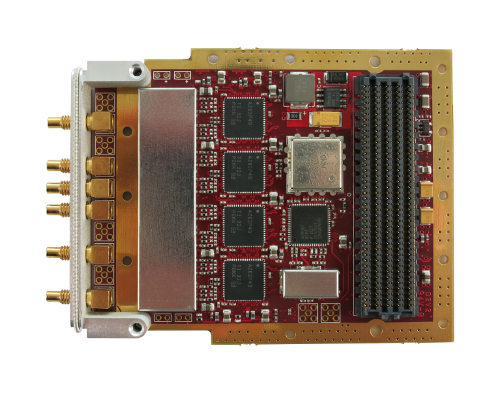

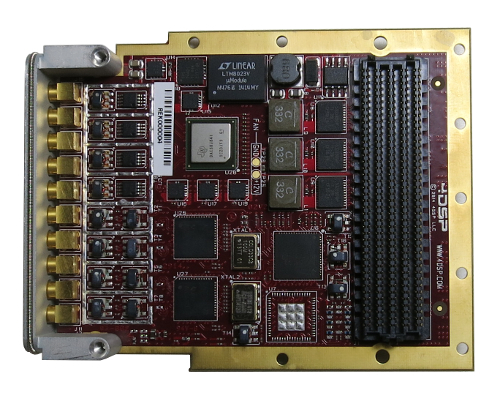

The following figures will present modern examples of finished and high-quality modules for analog-to-digital data conversion from Russian and foreign manufacturers. All of them have one or more analog input inputs and an FMC adapter (FPGA Mezzanine Card) connector for connecting to the carrier board on which the data processor is installed (usually it is FPGA). FMC is one of the main standards for connecting products in a modular architecture. The analog part is often installed on the mezzanine board (mezzanine board), and the central unit that carries out data processing is installed on the carrier module (carier board) - this is one or more FPGAs and / or signal processors. Among the foreign manufacturers of devices, two leading manufacturing companies should be distinguished - these are 4dsp and hitechglobal. Of the domestic manufacturers of Google in the first lines of the search, CJSC Scan Engineering Telecom, CJSC Instrumental Systems and others. The author of the articleis not responsible for the presented modules and does not use the article in order to advertise the product of a particular company.

HTG-ADC16 . It has the following characteristics (taken from the official site):

- 16-Bit Resolution, Dual-Chanel, 1-GSPS ADC

- Noise Floor: –159 dBFS / Hz

- Spectral Performance (fIN = 170 MHz at –1 dBFS):

- SNR: 70 dBFS

- SFDR: 86 dBc

- SFDR: 96 dBc (Except HD2, HD3, and Interleaving Tones)

- Spectral Performance (fIN = 350 MHz at –1 dBFS):

- SNR: 67.5 dBFS

- NSD: –154.5 dBFS / Hz

- SFDR: 75 dBc

- SFDR: 85 dBc (Except HD2, HD3, and Interleaving Tones)

- Channel Isolation: 100 dBc at fIN = 170 MHz

- Input Full-Scale: 1.9 VPP

- Input Bandwidth (3 dB): 700 MHz

- On-chip dip

- Integrated Wideband DDC Block

- JESD204B Interface with Subclass 1 Support:

- 2 Lanes per ADC at 10.0 Gbps

- 4 Lanes per ADC at 5.0 Gbps

- Support for Multi-Chip Synchronization

- Power Dissipation: 1.35 W / ch at 1 GSPS

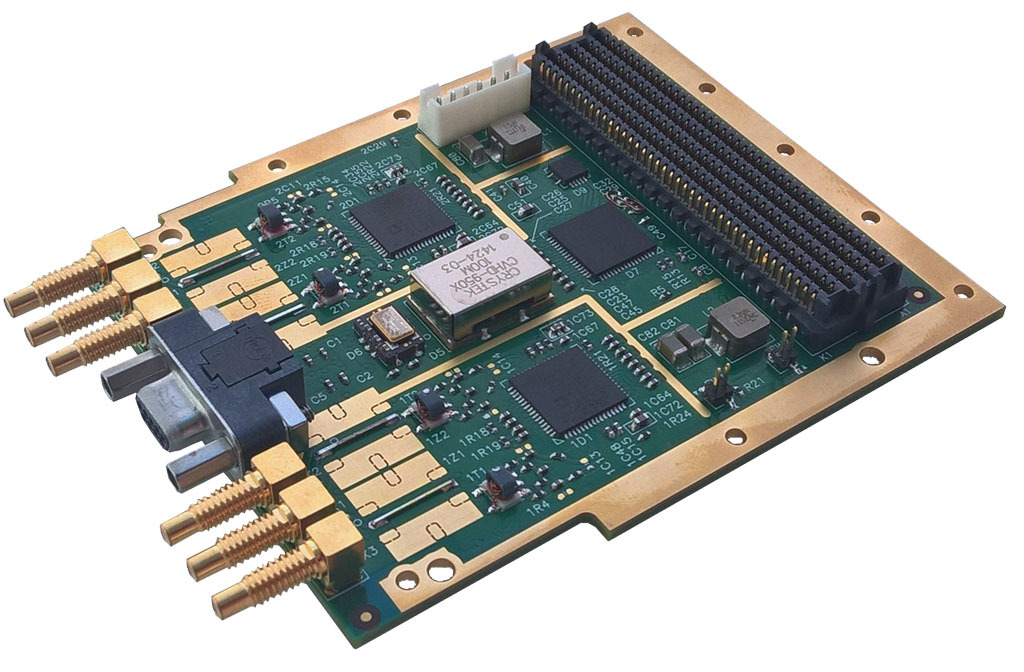

FMC104: 4-Channel 250 MSPS @ 14-bit . Characteristics (some deleted due to redundancy of information):

- Four Channel 14-bit 250 MSPS A / D conversion

- Available as air cooled and conduction cooled

- VITA 57.1-2010 compliant

- Based on TI ADS62P49

- LVDS or 1.8V LVCMOS output operation

- Single ended AC- or DC-coupled analog input

- Flexible clock tree enables

- LPC (low-pin count) compatible

The module features four ADC channels and a 1.8V power supply (HP Xilinx FPGAs are used).

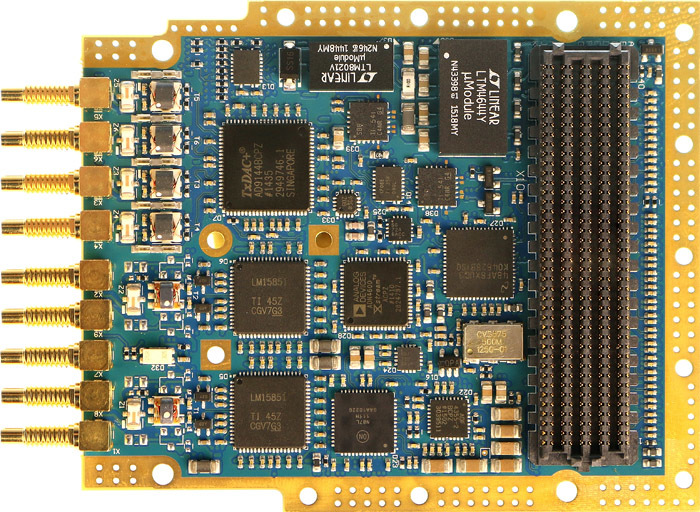

FMC120: 4-Channel 250 MSPS @ 14-bit . Specifications:

- Quad - A / D - D / A Channel Operation

- Quad Channels 16-bit 1.00 GSPS A / D

- Quad Channels 16-bit 1.25 GSPS D / A

- Simultaneous sampling on all channels up to 1 GSPS

- VITA 57.1-2010 compliant

- Conduction Cooled - Standard Option

- Single ended DC or AC-coupled analog input.

- Clock Source, Sampling Frequency, and Calibration through an SPI communication bus

- HPC - High Pin Count Connector

- 2Kbit EEPROM (24LC02B) accessible from the Host via I2C bus

- JTAG - CPLD device is included in the JTAG chain accessible from the FMC connection

FMC140: 4-channel 16 bit 370MSPS A-/ D . It has the following characteristics:

- Four-channel, 16-bit A / D up to 370 MSPS

- VITA 57.1-2010 compliant

- JESD204B serial interface

- AC or DC-coupled analog signals

- Clock source, sampling frequency, and calibration through SPI communication busses

- Flexible clock tree enables

- Power-down modes to switch off unused functions for system power savings

- HPC - High Pin Count connector

The module features 4 high-speed ADC channels, 16-bit data capacity, and JESB204B communication.

SFM-4A1000 module . Specifications:

- Four ADC channels: 14 bit 1000 MHz

- Up to 2 GHz wideband transformer input

- Interface with JESD204B carrier module

- Support for digital decimation and AGC functions built into the ADC

- Highly stable reference oscillator, external reference clock input

- Software control of ADC settings and clock circuit

- Single-Width FMC Form Factor with Air or Conductive Cooling

The module’s peculiarity is domestic development, 4 high-speed ADC channels, 2 GHz band, JESB204B interface exchange.

FMC212x4GDA module . Specifications:

- Two 12-bit ADC channels

- Conversion Frequency: 1 to 4 GSPS

- Analog input band: 5 to 2000 MHz

- Input Impedance: 50 Ohms

- DDC integrated in ADC

- Maximum DDC Bandwidth: 800 MHz

- Decimation coefficient DDC: 4 to 32

- Four channel DAC 16 bit 2.8 GSPS

- Interpolation: x2, x4, x8

- DAC Output Frequency Range: 0.5 to 400 MHz

- Maximum Output Amplitude: ± 0.5 V

- Output Impedance: 50 Ohm

- Synthesizer for low-noise ADCs and DACs

- ANSI / VITA 57.1 FMC module 69x76.5 mm

The module features 2 high-speed ADC channels, a signal bandwidth of up to 2 GHz, an exchange on the JESB204B interface, built-in DDC chips, 4 DAC channels.

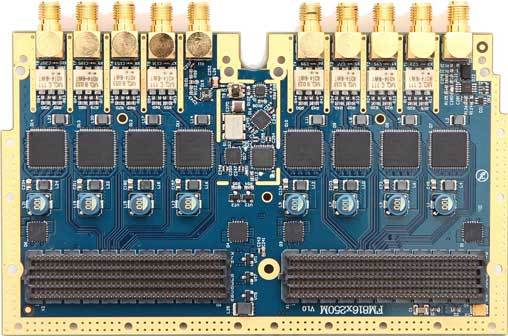

FMC816x250M module . Specifications:

- ANSI / VITA 57.1 FMC module double width 139x76.5mm

- 8 ADC 16 bit

- Conversion frequency: 50 MHz to 250 MHz

- Analog input band 0.1 ... 250 MHz

- Conversion Scales: ± 0.8V; ± 0.65V

- Input Impedance: 50 Ohms

- Internal / external clocking

- Tunable clock generator 10 ... 250 MHz

Feature of the module - 8 ADC channels, dual module.

As you can see, many of the analog-to-digital conversion modules in the FMC standard are similar and have almost identical characteristics, which are determined by the installed ADC and DAC chips. The final choice of a module is determined by the task that the end user needs to solve.

Connecting the ADC to the FPGA

Let's move on to the main section of the article - connecting ADC chips to FPGA crystals. Consider connecting an ADC on a parallel and serial bus, with data transfer interfaces - LVTTL, LVCMOS, LVDS . The article will not consider the connection of the ADC via the JESD204B interface , since this is material of a separate topic, which will take more than one full-fledged article. In addition, JESD204B differs significantly in implementation from the “classic” options for connecting ADC chips and requires a more detailed consideration.

As is known, FPGA I / O banks (pin groups) can be configured for different supply voltages, the boundaries of which are determined by the crystal manufacturer. In modern Xilinx FPGAs, the voltage range applied depends on the type of bank. There are two main types of bank (Xilinx) - HP (high-performance) and HR(banks with a large selection of standards and food). For example, in the Xilinx Series 7 chips, the voltage range for HR banks is from 1.2 to 3.3V, and for HP banks it is from 1.2 to 1.8V. In addition, bank pins can be programmed for a wide range of standard data transfer interfaces, but the final choice of standard is determined by two rules: the voltage of the FPGA bank and the method of connecting the remote device and the FPGA. On the other hand, a family of crystals is an important factor in choosing the supply voltage of the FPGA bank. So, for Kintex-7 it is possible to use the LVDS 25 standard and power the bank with a voltage of 2.5V, and for many Virtex-7 FPGAs the connection standard is exclusively LVDS 18, and the bank is powered by a voltage of 1.8V. In this regard, there is a problem of pairing some analog modules and carrier boards with different families of FPGAs. Therefore, when purchasing an ADC module and / or carrier board from a third-party manufacturer, you need to make sure that they are compatible with the standard and the supply voltage. As a rule, the data transfer interface is written in the restrictions file (UCF or XDC ), and not in the project source code, which provides configuration flexibility and reuse of source code files in other projects.

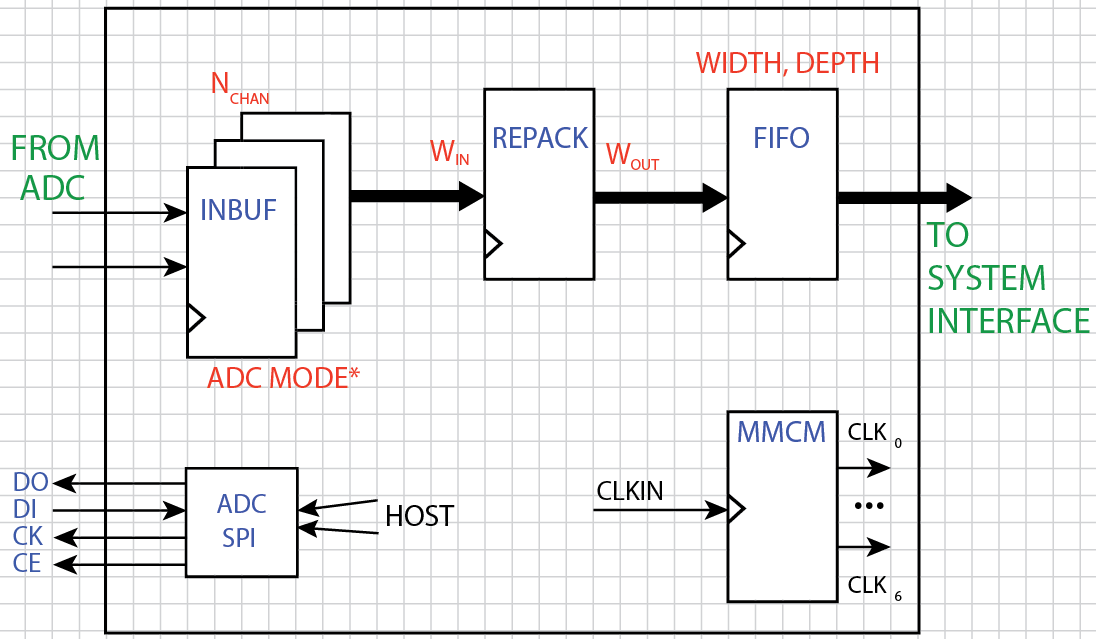

The structural diagram of the top-level file of the project (as well as the internal units used to receive data from ADC chips according to the LVTTL / LVCMOS / LVDS standard) is presented in the following figure.

It includes the following elements:

- Input receiver

- Data packer

- Data Stream Synchronizer (FIFO)

- ADC chip control unit

In addition to these nodes, at the upper level, a frequency synthesis module based on MMCM is used - a standard FPGA resource. Also, the IDELAYCTRL component is used to control delays in IODELAY nodes.

The main parameters of the top-level file on which the configuration of the circuit in the FPGA depends:

- NCHAN - the number of independent ADC channels,

- DATA_WIDTH - ADC data capacity,

- FIFO_ADDR - FIFO depth: DEPTH = 2 ** ADDR,

- DATA_RATE - data reception mode: SDR / DDR,

- PACK_OUT - width of the packer's output bus (system bus),

- CLK_SEL - selection of the main clock source for a multi-channel circuit,

- USE_MMCM - using the MMCM node instead of BUFR to divide the CLKDIV frequency by SERDES,

- DIFF_TERM - use of differential input signals (TRUE / FALSE),

- IOSTANDARD - voltage standard for LVDS lines,

- DATA_IOBDELAY_TYPE - operation mode of the delay node IODELAY,

- DATA_IOBDELAY_VALUE - default delay value,

- DIFF_CLOCK - use differential input signal (TRUE / FALSE),

- OVR_PRES - use of ADC overflow lines (overflow),

- STR_PRES - use of ADC external start signal lines (start),

- RESYNC_OUT - enable the mechanism of primary resynchronization of data on the input buffer (YES / NO).

And some other options.

Part of the code of the top-level file of the ADC receiver looks like this:

xFIFO: CTRL_FIFO_CONFIG

generic map (

DATA_WIDTH => PACK_OUT,

ADDR_WIDTH => FIFO_ADDR

)

port map (

reset => reset,

wr_clk => clk_pack,

rd_clk => sys_clk,

data_i => do_pack,

data_o => do_fifo,

rd_en => cs_fifo,

wr_en => dv_pack,

empty => ef_fifo,

full => ff_fifo

);

Here the FIFO node is connected to synchronize data with the system bus of the device. Programming delays for IODELAY in a multi-channel and multi-bit buffer circuit is as follows:

---- Data delays ----

x_dat_dd <= x_dat_do(conv_integer(unsigned(dl_chan))) when rising_edge(dl_clk);

x_dat_in(conv_integer(unsigned(dl_chan)))(conv_integer(unsigned(dl_muxs))) <= dl_dat_in when rising_edge(dl_clk);

x_dat_ce(conv_integer(unsigned(dl_chan)))(conv_integer(unsigned(dl_muxs))) <= dl_dat_ce when rising_edge(dl_clk);

x_dat_ld(conv_integer(unsigned(dl_chan)))(conv_integer(unsigned(dl_muxs))) <= dl_dat_ld when rising_edge(dl_clk);

Where dl_chan is the selected ADC channel, dl_muxs is the selected bit of the ADC. This is done to independently program each bit of data.

Consider each node in detail.

Note: for connecting FPGAs and DACs (digital-to-analog converters), the situation is mirrored. It is necessary to do the same thing, but in reverse order. In this article, the connection of the FPGA to the DAC is not considered.

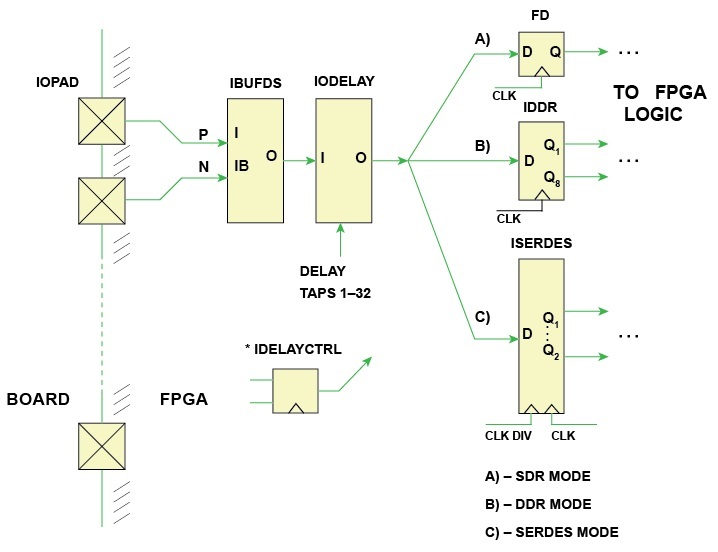

Input receiver

Contains the primary elements of the connection between external PCB signals and FPGA logic. This is the IPAD buffer from the FPGA pin to the IOBUF input buffer logic . Depending on the data transfer interface, the buffer can be differential - IBUFDS and unipolar - IBUF. For many buffers, a rigid binding to the required standard is possible, or it is possible to set the type of output signal through attributes. For example, for IBUFDS, using the IOSTANDARD attribute, you can predefine and set the standard “ LVDS_25 ” in the source codes .

Following the buffer, an IODELAY signal delay control unit is installedto align the edges of the parallel data bus and the initial coordination of multi-channel nodes connecting the ADC to the FPGA. IODELAY is a programmable FPGA resource, the delay value can be fixed and determined by the default setting, or programmed in the range from 0 to 31 conventional time values (the figure is determined by the datasheet on the FPGA chip). Programming is done in a primitive way with a few signals. We will not dwell on a detailed analysis of the programming algorithm; for more information, refer to the document from the list of references at the end of the article. For IODELAY nodes, a special IDELAYCTRL delay control node must be connectedwhich real-time calibrates delays for each FPGA clock region. To eliminate the influence of crystal temperature, supply voltage, and FPGA load, the IDELAYCTRL node is clocked by an independent REFCLK signal. This clock signal provides an equal amount of delay ( TAP ) in all IODELAY nodes of each FPGA clock region. If each clock region needs its own tuning values, several IDELAYCTRL nodes are initialized in the FPGA chip. The REFCLK clock signal can be supplied from an external generator installed outside the FPGA, or it can be obtained by synthesizing the frequency in the MMCM node of the FPGA chip.

Following the IODELAY delay node, it is possible to set the FD trigger if the data transfer mode is DATA_RATE = “ SDR ”. This trigger is optionally placed in the input buffer and is clocked by the frequency of the ADC accompanying the data from the analog module. In DATA_RATE = “ DDR ” mode , the trigger is replaced with a sophisticated version of IDDR , which has one data input and two outputs. It is possible to output data in several modes from the output, but in practice I used only one - “ SAME_EDGE_PIPELINED ”, in which data from the output Q1 and Q2 are output on the same edge of the clock signal.

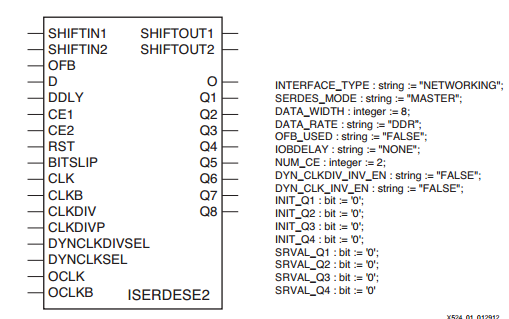

And finally, the most interesting option is to connect the IODELAY node to the ISERDES data deserialization module . The serializer node is a complex element of the FPGA input buffer; it contains the following options:

- DATA_RATE - defines the output data mode ( SDR / DDR),

- DATA_WIDTH - determines the width of the data bus at the node output (from 1 to 8),

- INTERFACE_TYPE - type of data transfer interface. To connect the ADC chips, the NETWORKING mode is used .

- SERDES_MODE - ISERDES connection mode in case of using several serializers to receive data from one FPGA contact.

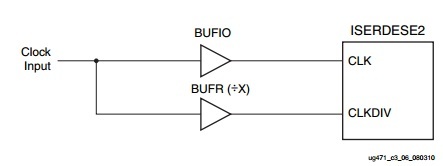

The node is clocked by several signals - this is a signal at a high frequency of received CLK data and a CLKDIV signal divided by the number determined by the DATA_WIDTH parameter. Division can occur outside the FPGA, but in practice, frequency synthesizers are used in the FPGA chip itself, which are called MMCM. Thus, a serial signal at the CLK frequency is input to the ISERDES node, and a parallel data stream at a reduced frequency CLKDIV = CLK / DATA_WIDTH is obtained at the output of the ISERDES node . The clock frequency can be divided using the regional buffer BUFR , the value of the division coefficient BUFR_DIVIDE= 1-8, or on the node of the frequency synthesizer MMCM , programmable in a wide range.

To eliminate the effect of coincidence of the clock edge and data, IODELAY nodes and frequency tuning in MMCM are not always enough. Often you have to look for alternative solutions to this problem. Fortunately, this solution was found by my colleague, which he recently spoke about in his article ( Useful Properties of Jitter ).

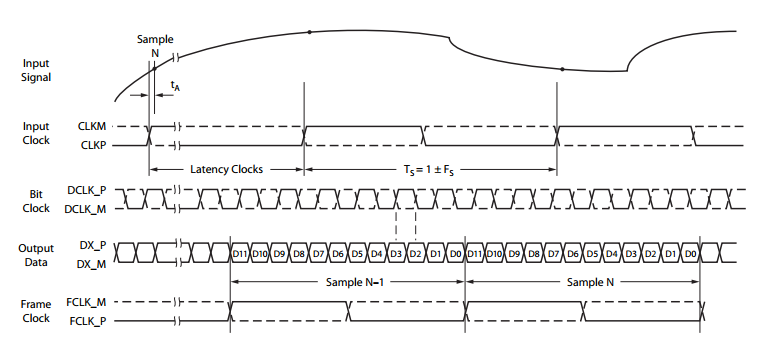

All of the above nodes (with the exception of MMCM) are part of the input FPGA buffer and do not occupy the logical resources of the chip. From the FD / IDDR / ISERDES output, the data already goes to the logical elements - this is a small trigger or FIFO for the primary resynchronization of the data to the frequency obtained after passing the ADC sampling frequency in the MMCM node. In some cases, resynchronization is not used, and the data is synchronized directly with the sampling frequency of the ADC. The following figure shows a timing diagram of processing serial data from an ADC chip on an ISERDES device. The input clock frequency, the serial form of the input data, and the converted data into parallel code are shown.

Thus, depending on the configuration, three signal paths are possible in the input buffer, as shown in the figure:

A) SDR mode - data is received on the parallel bus, each FPGA uses its own FPGA buffer,

B) DDR mode - data is received on the parallel bus, data is clocked at double frequency.

C) SERDES mode - data is received on the serial bus

Data packer

This node is used in single-channel and multi-channel schemes for receiving data from the ADC. Its main purpose is to pack the data into a convenient internal bus format used inside the FPGA. The capacity of the internal bus is determined by the developer or the corporate standard. Typical bit values at the output of the packer are 32, 64, 128, 256, 512 bits of data. In some cases, the packer may not be configured. It depends on the number of input channels, the width of the input and output data bus packer. For example, for a four-channel source with input bit depth = 16 bits, it is impossible to organize a repacker with an output bus bit less than WOUT = WIN * NCHAN= 16 * 4 = 64 bits. For a single-channel data source with the same bit depth at the input and output, the data will be sequentially packed in packets of 16 bits into a bit grid of 64 bits. That is, the first sample of the ADC will take the bit field [15: 0], the second sample - [31:16], the third - [47:32], and the fourth - [63:48]. Further, the samples will cyclically occupy bit fields from the lowest to the highest in the output data grid. Another example. 2 data channels are used, the bit widths at the input and output remain the same - 16 and 64 bits, respectively. If the data collection system on the remote device includes only one channel, then packing occurs as shown in the example above, and it does not matter which channel is turned on. If the acquisition system includes both channels, then the data is packaged in pairs from the younger part of the bit grid to the older one. The first countdown of the first channel will take the position [15: 0], the first countdown of the second channel will take the position [31:16], the second countdown of the first channel - [47:32], the second countdown of the second channel - [63:48]. As practice has shown, this is the most convenient option for packing data in multi-channel processing, in case of disconnection of certain transmission channels. Note: the number of channels must be a multiple of the power of two - 1, 2, 4, 8, etc. It may seem that this node is difficult to implement and understand, but after several applications in your projects you will find for yourself that there is nothing complicated and unusual here. in case of disconnection of certain transmission channels. Note: the number of channels must be a multiple of the power of two - 1, 2, 4, 8, etc. It may seem that this node is difficult to implement and understand, but after several applications in your projects you will find for yourself that there is nothing complicated and unusual here. in case of disconnection of certain transmission channels. Note: the number of channels must be a multiple of the power of two - 1, 2, 4, 8, etc. It may seem that this node is difficult to implement and understand, but after several applications in your projects you will find for yourself that there is nothing complicated and unusual here.

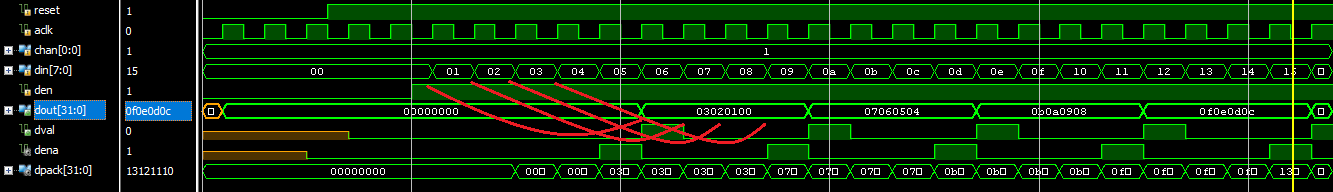

The following figure shows the timing diagrams of the operation of the data packer node in the mode: NCHAN = 1, WIN = 8, WOUT = 32.

The red lines show the process of packing data onto the output bus, which is accompanied by a resolution signal DVAL = 1 after receiving 4 data samples.

Data stream synchronizer

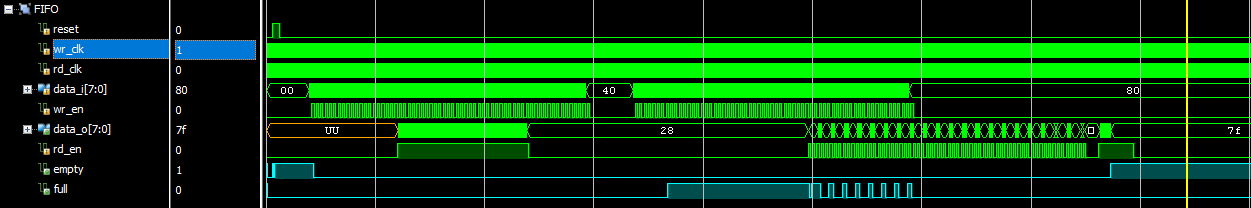

This node is built on the basis of a primitive FIFO scheme and has one important and simple purpose - converting the data stream from the sampling frequency CLK_ADC to the processing frequency or the operating frequency of the internal bus of the SYS_CLK device (system clock frequency). For simplicity, you can create a FIFO node in the Xilinx Core Generator , but ideally it is better to write your own module, which will be flexible in configuration for an arbitrary bus width ( FIFO_WIDTH ) and memory depth ( FIFO_DEPTH ). The following figure shows the timing diagrams of the operation of the FIFO node, shows the input and output data, as well as the flags empty ( empty ) and full ( full) FIFO. It should be noted that for normal operation of the FIFO ADCs, the FULL flag must always be 0, which indicates the correctness of data reception from the ADC and the absence of overflow. If the flag FULL = 1, then the speed of receiving data by the remote handler is insufficient, or the speed of the ADC is too high for the selected system.

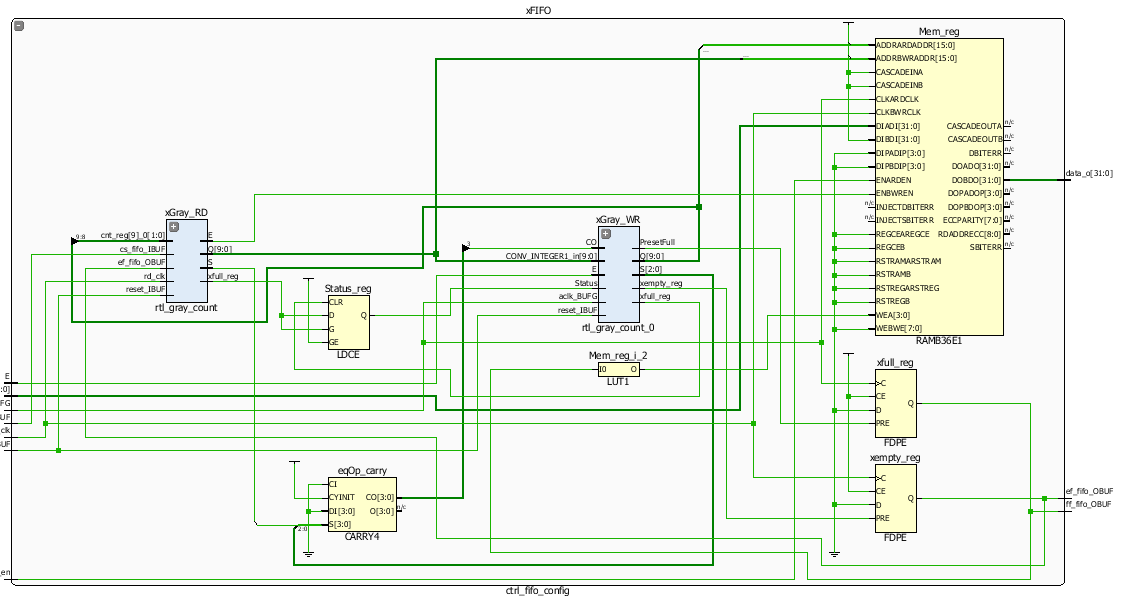

The following figure shows a schematic representation of a FIFO node in a Plan Ahead environment.

It can be seen that FIFO is built on the basis of dual-port memory. Data in Gray code is sent to the memory address buses - in the diagram, these are two nodes for reading and writing. This allows you to reduce the bit error at high frequencies, because adjacent values in the Gray code differ in only one bit position. The logic of the FIFO flags is determined by the values in the modules of the Gray counter, and registers are used to increase the clock frequency of the node at the output.

Inner tire

The question arises - where do the collected and packaged data go next ? The answer is simple: with the help of PCI / PCIe, USB, Ethernet, SRIO, SATA interfaces, data reach the final goal, where they are processed and where all the information is collected. Prior to this link, there can be a digital signal processing unit (DSP) inside the FPGA, for example, DDC, DUC, FFT / IFFT , etc. In addition, data can be buffered on a large external memory such as DDR3 / DDR4. This is a frequent technique that is used to process a large flow of information at high speeds. In this case, the external memory simulates a large FIFO. To control the FPGA with external memory, special controllers are used, which, as a rule, are accessible and open for use. In the case of Xilinx, they are in the IP Core Generator.

Among other things, the developer needs to create his own finite state machineall resources of the ADC receiver: this is the delay configuration in IODELAY, programming the MMCM frequency synthesizer, sending SPI commands to the ADC and DAC modules, controlling the beginning and end of data collection from the ADC, controlling the number of active channels, using external DDR memory and much more. Everyone has their own unique architecture, but the basic principles remain the same. The company in which I work uses control nodes called notebooks . Details about them were told by my colleague here .

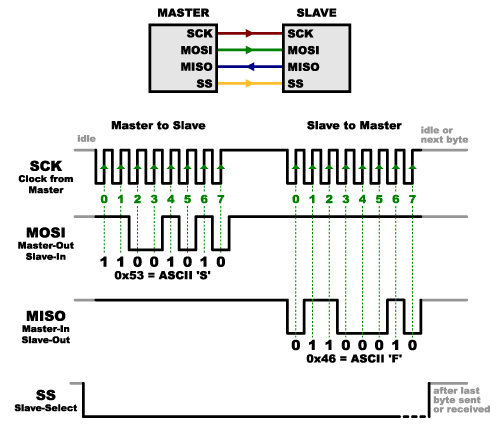

ADC module control

As a rule, the analog module is controlled via SPI-like interfaces. Implement an SPI interface for any senior student whose program includes the study of programmable logic and FPGA. I will not focus on the SPI node. At the end of the article, an example is given of the source code for controlling a remote microcircuit HI-6131 , which processes messages in the MIL-STD-1553 format . The code is not parameterizable and specifically tailored to the selected chip. To warm up, you can write your SPI node, which will be configured for different parameters. The SPI interface control timing chart is as follows:

Source

The source code of all components and nodes is presented in the VHDL language and is intended for Xilinx 7-series FPGA chips (and higher). Source codes are open for use and are available via the link on the github - see here . All components are made as flexible as possible in the configuration and do not require significant intervention in the source code (except for the SPI node -

For example, the read and write operations in FIFO, as well as the connection of the nodes for converting binary code to Gray code, are as follows:

FIFO R / W

---- Read data ----

pr_rd: process(rd_clk) begin

if (rising_edge(rd_clk)) then

if (rd_en = '1' and xempty = '0') then

data_o <= Mem(conv_integer(pNextWordToRead));

end if;

end if;

end process;

---- Write data ----

pr_wr: process (wr_clk) begin

if (rising_edge(wr_clk)) then

if (wr_en = '1' and xfull = '0') then

Mem(conv_integer(pNextWordToWrite)) <= data_i;

end if;

end if;

end process;

---- Gray counters ----

xGray_WR : rtl_gray_count

generic map ( COUNTER_WIDTH => ADDR_WIDTH )

port map (

cnt => pNextWordToWrite,

ena => NextWriteAddressEn,

rst => reset,

clk => wr_clk

);

xGray_RD : rtl_gray_count

generic map ( COUNTER_WIDTH => ADDR_WIDTH )

port map (

cnt => pNextWordToRead,

ena => NextReadAddressEn,

rst => reset,

clk => rd_clk

);

List of references

- 7 Series FPGAs Overview (DS180) (xilinx.com)

- Xilinx 7 Series Libraries Guide for Schematic Designs (xilinx.com)

- 7 Series FPGAs SelectIO Resources User Guide (UG471) (xilinx.com)

- 7 Series FPGAs Clocking Resources User Guide (UG472) (xilinx.com)

- Serial LVDS High-Speed ADC Interface (xilinx.com)

- Analog for Xilinx ® FPGAs Selection Guide (ti.com)

- HSC-ADC-FPGA High Speed Deserialization (analog.com)

- Interfacing Analog to Digital Converters to FPGAs (latticesemi.com)

To be continued...