IBM Introduces World's First Three-Bit PCM Memory

The specialists of our company at the annual thematic forum IEEE International Memory Workshop in Paris presented a working prototype of memory based on a phase transition (Phase-change memory, PCM). Each memory cell contains three bits of data. The test sample was created using the 90-nm CMOS process technology and is presented as an array with a capacity of 32 Mbit.

According to the developers, such a memory is very promising, since it is able to withstand several million write cycles. At the same time, ordinary flash-memory - no more than 3000 cycles of rewriting. The speed of PCM memory is approximately equal to the speed of RAM. If development can be launched into mass production, this will make it possible to obtain universal memory, and in the not too distant future. Well, now the company plans to use PCM chips for SSDs, as well as buffer memory for SSDs with NAND flash as the basis.

Interestingly, PCM memory alone is not new. But this development has not yet received wide distribution due to its main problem - low recording density. The three-bit PCM cell solves this problem. Previously, Intel and Micron tried to solve the problem of low recording density of PCM memory by introducing a multi-layer 3D structure in the form of 3D XPoint memory. Yes, this is also a solution to the problem, but three-bit memory is cheaper and somewhat easier to manufacture. In addition, a single-layer structure is more reliable than a multi-layer one, and in the latter case, mass production is fraught with the risk of a large number of defective elements.

How PCM memory works

Compounds that are used in this type of memory have two physical states - amorphous (without a clearly defined crystalline structure) and crystalline (where this structure is clearly visible). The transition from one state to another occurs when an electric current is applied to a compound. An amorphous state with high resistance is used to represent binary 0, and a crystalline state with a low level of resistance is 1.

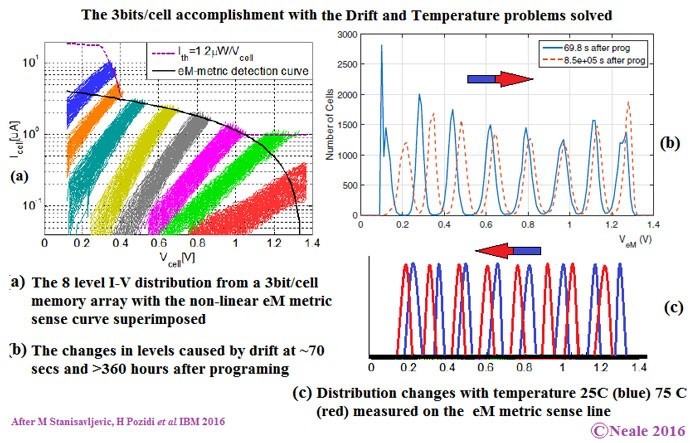

In order to store 0 or 1 in memory, it is necessary to use an electric signal (strong and medium for 0 and 1, respectively). In order to read a bit of information, you need to use a low voltage. The volume of the substance transferred in the memory cell from the initial amorphous to crystalline state to a large extent depends on the applied current strength. Reading from such a memory occurs using low currents. To write 3 bits in one cell, you need to use a rather complex 8-level signal.

Previously, as mentioned above, various research teams sought to save one bit of information in the memory cell. But now, the specialists of our company managed to save three bits in the cell.

The effect of temperature on PCM memory

The new development uses two approaches. The first is the development of a reference signal to determine the level of recording in the cell. The second is the use of special methods for programming recording levels. Previously, PCM memory, in addition to the certain complexity of working with it, had another problem - exposure to temperature. Because of this, over time, the record level in the cell "floated", the information became poorly readable. Now our specialists have managed to solve this problem, and the temperature no longer presents such a serious problem as before.

There is no talk about the commercial use of the technology, but in the near future, perhaps, a new type of PCM memory will become the standard. Initially, we plan to release several test samples, and then arrange the production of commercial systems.