Intel Xeon processors equipped Altera FPGA

Intel begins shipping a dual-chip development platform consisting of the Xeon E5-2600 v4 processor (Broadwell) and the Altera Arria 10 FPGA - this information was voiced by Intel vice president Diane Bryant in his speech at the IDF 2016 conference in China . It is assumed that with the help of such a hybrid it will be possible to obtain a 70% increase in performance at the same power consumption and frequency. The fruits of cooperation between Intel and Altera, which lasts far from the first year, we have already seen in the face of the prototype 5G platform- FPGA and Intel Core crossed there. And now - a new duet. Future plans include full integration of both components on a single chip. The first consumers of the hybrid will be the largest cloud services and data centers. According to Intel forecasts, by 2020 up to 30% of servers in data centers will have processors with FPGA.

Intel begins shipping a dual-chip development platform consisting of the Xeon E5-2600 v4 processor (Broadwell) and the Altera Arria 10 FPGA - this information was voiced by Intel vice president Diane Bryant in his speech at the IDF 2016 conference in China . It is assumed that with the help of such a hybrid it will be possible to obtain a 70% increase in performance at the same power consumption and frequency. The fruits of cooperation between Intel and Altera, which lasts far from the first year, we have already seen in the face of the prototype 5G platform- FPGA and Intel Core crossed there. And now - a new duet. Future plans include full integration of both components on a single chip. The first consumers of the hybrid will be the largest cloud services and data centers. According to Intel forecasts, by 2020 up to 30% of servers in data centers will have processors with FPGA. It is worth mentioning here that last year Intel and eASIC launched a joint project to create the Xeon + ASIC platform for customizing processors for specific pre-specified loads. Truly, more Xeons, good and different!

Under the cat - some information about the FPGA Altera Arria 10.

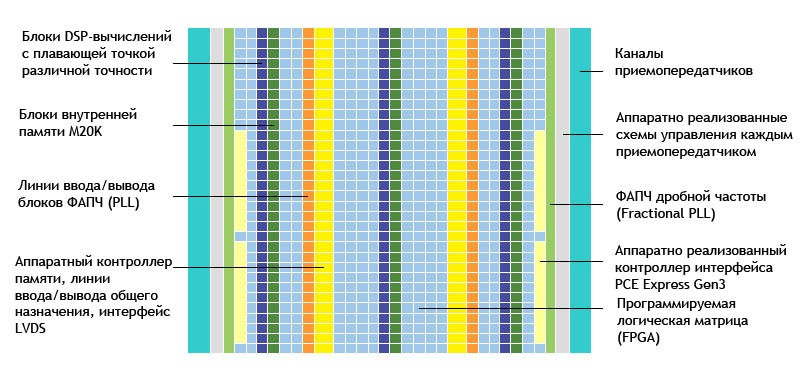

FPGA device Arria 10 family

The new FPGAs of the Arria 10 family are made according to technological standards of 20 nm. Arria 10 family devices are up to 40% less energy efficient than previous generation FPGAs and are the only programmable logic circuits in the industry with hardware-based digital signal processing units for floating-point signals with a capacity of 1,500 GFLOPS (billion floating-point operations).

- Integrated Transceiver Bandwidth up to 28.3 Gbps

- 2666 Mbps high-performance external memory interface

- Floating-Point DSP Hardware Blocks Compliant with IEEE 754

- Up to 96 transceiver channels provide a serial data path with a throughput of up to 3.6 Tbps

Programmatic use of FPGA capabilities will be implemented through Altera OpenCL SDK