PCIe 5.0 bus is ready for commissioning

- Transfer

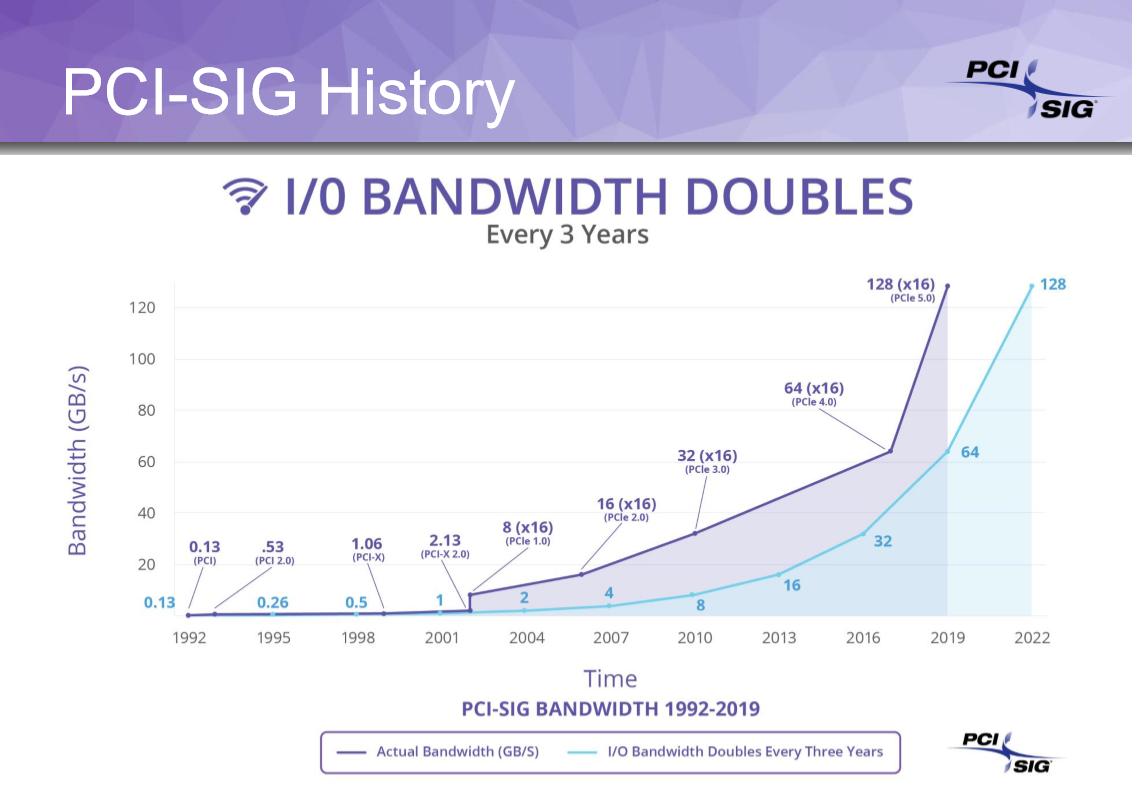

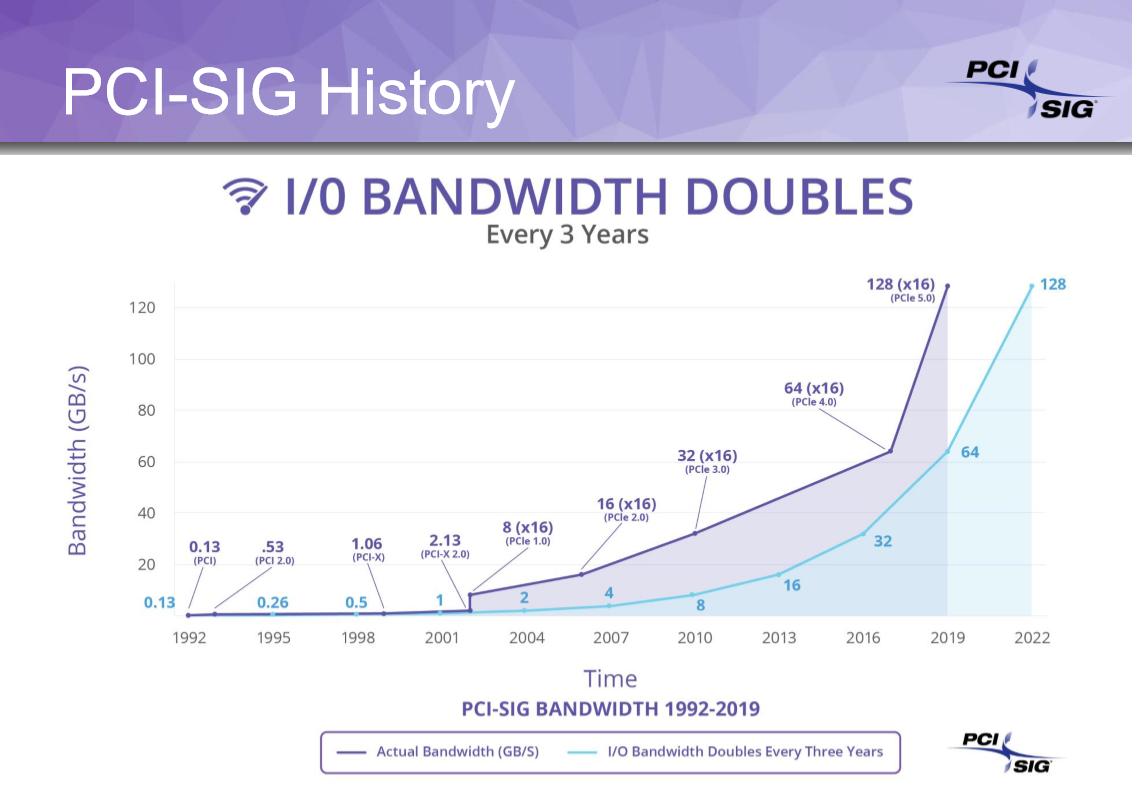

The industry has been stuck with a PCIe 3.0 bus for almost seven years, and although the first PCIe 4.0 support for desktop computers will soon appear in AMD's third-generation Ryzen chip, and the first PCIe 4.0-enabled SSDs have appeared quite recently , manufacturers are already preparing to adopt PCIe 5.0. The new standard doubles the bandwidth compared to PCIe 4.0, which gives a speed of 32 GT / s [ transactions per second ].

Today, PCI-SIG, an organization that defines PCIe standards, has announced the adoption of the specification of version 0.9 for the PCI Express 5.0 bus, which means that end devices will appear on the market in the near future. (Companies are starting to develop ready-made devices with the specification of version 0.4, and with the advent of version 0.9, many are already launching their products).

PCIe is used everywhere and pulls on itself a tangible part of computing, as concerns almost all devices that are in your computer. Because of this, it serves as a catalyst for the development of many other technologies, for example, data storage, network technologies, GPU, chipsets, etc.

Unfortunately, the PCIe 4.0 standard was strongly delayed relative to the usual PCI-SIG rhythm, which produced something approximately once every two years. PCIe 3.0 was approved in 2010, and there was a seven-year gap between it and the advent of PCIe 4.0. Given the rapid emergence of the PCIe 5.0 standard, it is easy to assume that it will not live long, especially given the fact that manufacturers have already started developing devices with the new protocol of the physical layer PCIe 5.0.

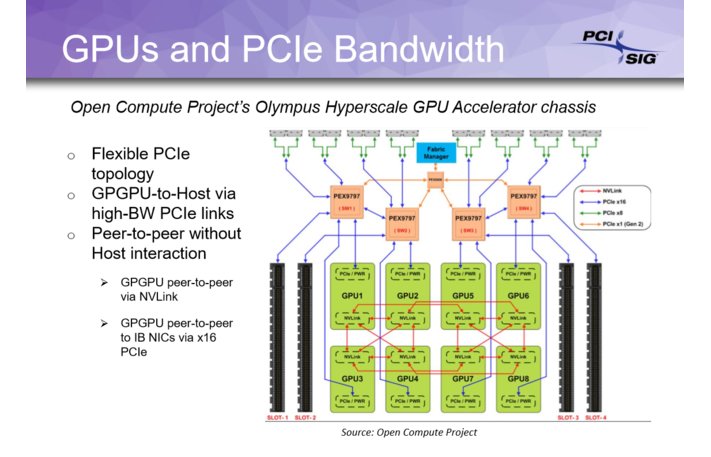

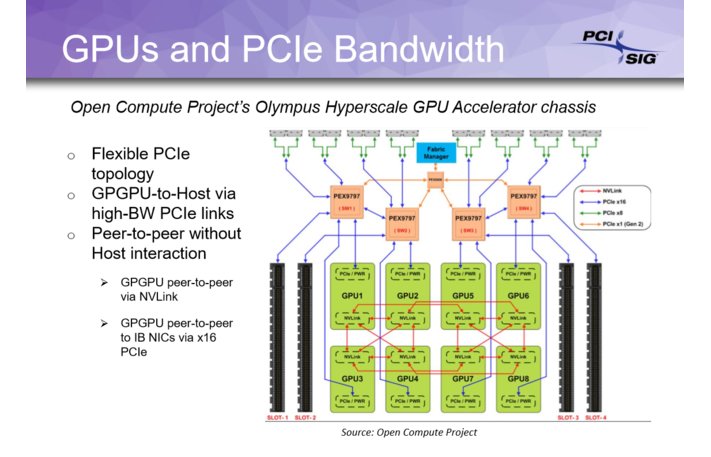

In PCI-SIG they expect that for some time these two standards will exist in parallel, PCIe 5.0 will be used in the fastest devices that require maximum throughput, for example, in working with GPUs that deal with AI and network technologies. So, many of the advanced devices with support for PCIe 5.0 will appear in data centers, network environments and high-performance computing; less demanding applications, like home PCs, will be content with a PCIe 4.0 interface.

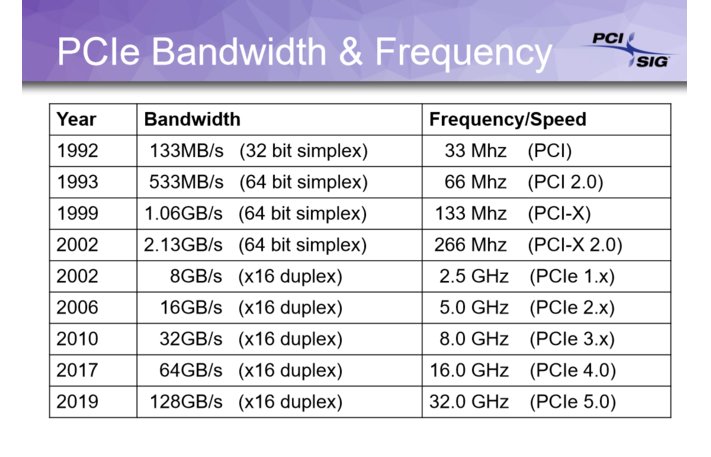

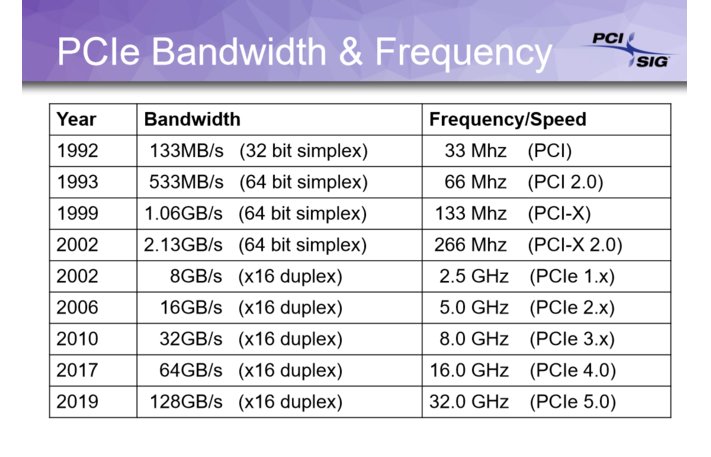

PCIe bandwidth and frequency

Ethernet evolution

GPU and PCIe PCIe 5.0 bandwidth

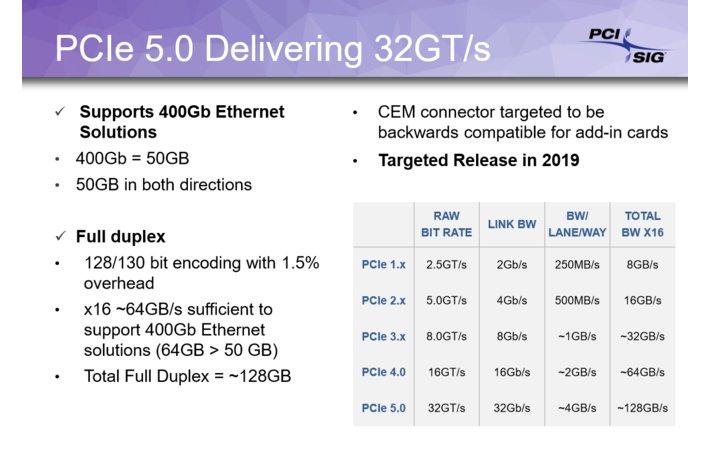

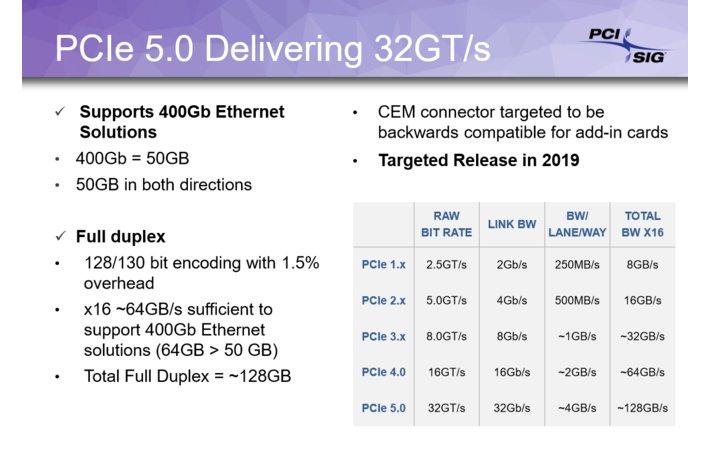

will deliver 32 GT / s

PCIe 4.0 provides 64 Gb / s bandwidth and PCIe 5.0 doubles it to 128 Gb / s. Both versions will use the 128b / 130b coding scheme, introduced in the PCIe 3.0 standard. Representatives of PCI-SIG stated that they were quite satisfied with a decrease of 20% overhead when using 128b / 130b coding, and that further coding improvements would result in a negligible gain of 1.5%.

In PCIe 5.0, other options will appear, such as changes in electronics to improve signal clarity, backward-compatible CEM connectors and backward compatibility with previous versions of PCIe. PCI-SIG also developed a new standard that reduces latency and is more resistant to signal loss.

PCI-SIG determines the specification, but does not control when exactly ready devices will appear on the market. PCI-SIG is awaiting approval of the final specification version 1.0 in the first quarter of 2019, and the release of the first devices with support for PCIe 5.0 during this year. In 2020, an increase in their prevalence is expected.

Today, PCI-SIG, an organization that defines PCIe standards, has announced the adoption of the specification of version 0.9 for the PCI Express 5.0 bus, which means that end devices will appear on the market in the near future. (Companies are starting to develop ready-made devices with the specification of version 0.4, and with the advent of version 0.9, many are already launching their products).

PCIe is used everywhere and pulls on itself a tangible part of computing, as concerns almost all devices that are in your computer. Because of this, it serves as a catalyst for the development of many other technologies, for example, data storage, network technologies, GPU, chipsets, etc.

Unfortunately, the PCIe 4.0 standard was strongly delayed relative to the usual PCI-SIG rhythm, which produced something approximately once every two years. PCIe 3.0 was approved in 2010, and there was a seven-year gap between it and the advent of PCIe 4.0. Given the rapid emergence of the PCIe 5.0 standard, it is easy to assume that it will not live long, especially given the fact that manufacturers have already started developing devices with the new protocol of the physical layer PCIe 5.0.

In PCI-SIG they expect that for some time these two standards will exist in parallel, PCIe 5.0 will be used in the fastest devices that require maximum throughput, for example, in working with GPUs that deal with AI and network technologies. So, many of the advanced devices with support for PCIe 5.0 will appear in data centers, network environments and high-performance computing; less demanding applications, like home PCs, will be content with a PCIe 4.0 interface.

PCIe bandwidth and frequency

Ethernet evolution

GPU and PCIe PCIe 5.0 bandwidth

will deliver 32 GT / s

PCIe 4.0 provides 64 Gb / s bandwidth and PCIe 5.0 doubles it to 128 Gb / s. Both versions will use the 128b / 130b coding scheme, introduced in the PCIe 3.0 standard. Representatives of PCI-SIG stated that they were quite satisfied with a decrease of 20% overhead when using 128b / 130b coding, and that further coding improvements would result in a negligible gain of 1.5%.

In PCIe 5.0, other options will appear, such as changes in electronics to improve signal clarity, backward-compatible CEM connectors and backward compatibility with previous versions of PCIe. PCI-SIG also developed a new standard that reduces latency and is more resistant to signal loss.

PCI-SIG determines the specification, but does not control when exactly ready devices will appear on the market. PCI-SIG is awaiting approval of the final specification version 1.0 in the first quarter of 2019, and the release of the first devices with support for PCIe 5.0 during this year. In 2020, an increase in their prevalence is expected.