Life in the era of "dark" silicon. Part 1

Other parts: Part 2 . Part 3 .

While the continuation of the story about communication factories is postponed for reasons beyond my control, I would like to cover another topic.

From October 8 to October 12, the largest conference in Russia devoted to the problems of developing micro- and nanoelectronic systems was held in the Moscow Region. And although the conference itself left a rather negative impression, one of the speeches stood out from the crowd and would probably be interesting to dear readers. This is an analytical report "Life with" dark "silicon. Power and termal problems in future platforms ”, represented by Mike Kishinevsky (Principal Engineer, Strategic CAD Labs, Intel Corp.). I will try to talk about the main ideas of this report using conference materials and third-party sources.

What is "dark" silicon

So, as everyone knows, back in 1965, Gordon Moore, one of the founders of Intel Corporation, formulated an observation, later called the “Moore's Law”. [1] According to this observation, the number of transistors placed on a silicon crystal doubles approximately every two years. This trend has persisted for more than 45 years, thanks to the advent of increasingly complex processes. Now 22nm technical process is actively used, 14nm will appear in the next 1-2 years, and 10nm is also just around the corner. [2]If this trend continues, then by 2022 the number of transistors inside one chip will reach a trillion, and the number of metallization layers (used to form links between transistors) will reach 14-18 pieces - this is necessary in order to effectively combine such a huge number of transistors into a single system . [3] But, unfortunately, not everything is so cloudless.

According to the dependence, known as Dennard’s law, when scaling the technical process S times, the computing power (under ideal conditions) increases as S 3 . In addition, such growth occurs without additional energy overhead. This is because in the same area it is placed in S 2more transistors that do useful work, and such transistors can operate at a higher clock speed. In this case, the capacitance and operating voltage can be reduced by S times. [4]

In practice, as the process decreases, leakage currents flowing through a closed transistor increase, which is the main factor in the growth of energy consumption, which in the ideal case would not change. As a result of this growth, in the two thousandth heat dissipation of some processors was approaching what can be observed in the bowels of a nuclear reactor, and energy consumption was associated more with a welding machine, rather than with a high-tech device. [5]

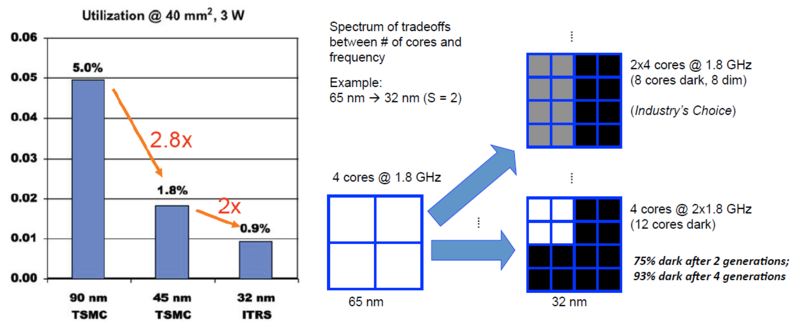

The need to remain within certain limits of energy consumption led to the appearance of a restriction called Utilization Wall, according to which, with each new technological process and in the absence of radical technological changes, the fraction of the crystal area involved in active work (literally, where transistors can switch) decreases exponentially. Moreover, this area is measured in units or even fractions of a percent. [6] The remaining most part of the crystal, which was not currently involved in the work, was called “Dark” Silicon.

Utilization Wall

As a result, developers of new microprocessors must be sure that at any time most of the crystal is “dark” or “dull” silicon - it is inactive or operates at a significantly lower clock frequency.

Michael Taylor in his article “Is Dark Silicon Useful? Harnessing the Four Horsemen of the Coming Dark Silicon Apocalypse "[7] mentions the four" riders of the Apocalypse "- four basic approaches that allow microelectronics to flourish in the era of" dark "silicon. These approaches: using new technological advances, parallelization for energy efficiency, specialization and energy management. In addition, system-level optimization plays an important role. These approaches will be discussed further.

“The Deus Ex Machina Horseman” or Process Progress.

“MOSFETs are the fundamental problem. “

We can switch to FinFets, Trigate, High-K,

nanotubes, 3D, for one-time improvements,

but none are sustainable solutions across

process generations.

Of all four riders of the silicon apocalypse, this is by far the most unpredictable. In literature or theater, Deus Ex Machina refers to a plot in which the main characters seem completely doomed, but then something completely unexpected and unpredictable comes out of nowhere to save the situation.

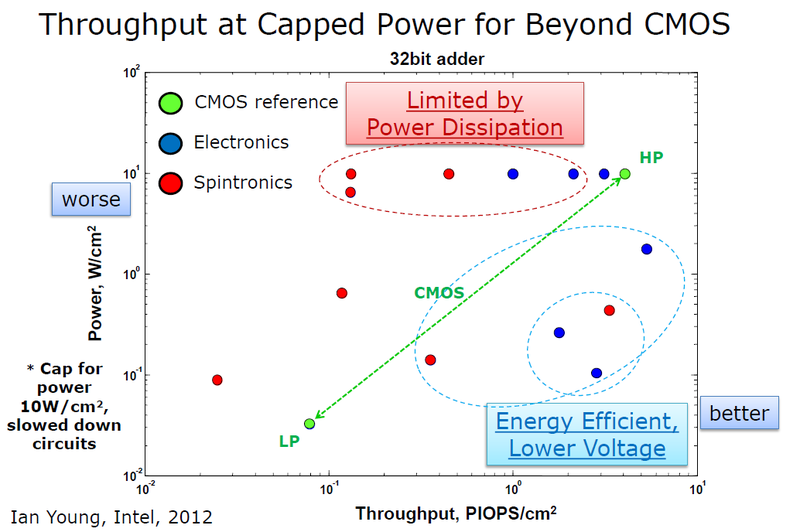

In the case of dark silicon, Deus Ex Machina could be a scientific breakthrough in semiconductor technology. However, such breakthroughs should be quite fundamental. And, most likely, in the near future, such a breakthrough will require the use of transistors other than traditional MOSFET technology. The reason is that leakage currents are determined by fundamental physical principles. While innovations such as the invention of FinFET / Tri-Gate transistors or the use of High-K dielectrics, etc., represent significant achievements. But they are more likely to be one-time improvements, not scalable changes. [8] I will not dwell on the benefits of Tri-Gate, as more than once was written about them :)

The development of technologies that can replace the MOSFET has been ongoing for a long time. Two potential and (at the moment) the most promising candidates: these are TFET transistors and nano-electro-mechanical switches. There are reasons to believe that both of these technologies can reduce leakage currents by orders of magnitude compared with the solutions currently in use, but at the same time, they are still very far from industrial use.

One source of optimism about the existence of breakthrough technologies is the performance, energy efficiency and density of the human brain. The brain combines 100 trillion synapses that work by consuming less than 20W, and serve as living proof of the possibility of highly parallel and at the same time mostly “dark” calculations.

As a result, technological advances still continue to amaze; now there are a number of interesting alternatives to traditional MOSFET electronics. But to predict when these alternatives get to industrial use, and even more so, the appearance of new ones is not possible.

The Shrinking Horseman and parallelization for energy efficiency

“Area is expensive. Chip designers will

just build smaller chips instead of having

dark silicon in their designs! ”

(If you work on Dark Silicon research, you will hear this a lot ...)

Due to the increase in leakage currents as the process scales, the multi-core microprocessors can no longer scale in the same way as the crystal area occupied by a single core decreases. At the same time, “dark” or “dull” silicon is an exponentially cheaper resource in terms of energy consumption. This makes us turn to architectural solutions that allow us to “expend” the area of the crystal in order to “acquire” energy efficiency. The example shown in the figure shows how replacing one comparator with two, working in parallel, but at half the frequency, can reduce power consumption by 2.5 times! [9] In practice, not all nodes can be parallelized in a manner close to ideal, but the gain in terms of energy consumption will still be noticeable.

Trade-off area and energy consumption

An immediate reaction to this approach from many developers was that "the area of the crystal is an expensive resource, why not just make microprocessors smaller instead of using" dark "silicon?" However, this is the most pessimistic scenario. And although all chips may ultimately undergo a reduction in area, this view misses a number of secondary factors that play a decisive role.

Firstly, it is worth saying that “dark” silicon does not mean “empty”, “useless” or “unused”silicon. Even in the best days of CMOS technology, the microprocessor and other circuits were full of dark logic, which is used only for some tasks. For example, the x86 SSE instruction execution block is not used for irregular calculations, and doubling LLC (the last level of the cache) gives a gain only for a small range of tasks.

Also noteworthy is the financial side of the reduction in crystal area. There is some truth to the fact that producing smaller crystals is more profitable. In the end, microprocessor developers spend a lot of effort trying to get into the affordable budget for the footprint. Smaller processor crystals are linearly (or even more) cheaper. In addition, they have higher yield rates in production. But exponentially smaller processors will not be exponentially cheaper due to the costs of developing, manufacturing lithographic masks, packaging, etc. And these costs should also somehow be amortized, which will lead to an increase in cost per unit area of silicon. Which, in turn, will make the transition to a new process less financially attractive and lead to an unhappy economic end to Moore’s law. There are also a number of other reasons based on the laws of a competitive economy,

Well, one cannot fail to mention the problems associated with packaging and heat dissipationarising from a reduction in the area of the crystal. An important consequence of the exponential reduction in area is the exponential increase in specific power consumption. Recent studies in the analysis of the thermal characteristics of multicore processor chips [10] have shown that the peak temperature of a hot spot (hotspot) can be modeled as Tmax = TDP * (Rconv + k / A). Where TDP is the value indicating the heat output for which the cooling system of the processor is designed, Rconv is the heat sink characteristic (less is better), k is the collective characteristic of the microprocessor's properties, and A is the occupied area. With an exponential decrease in area, the second term becomes dominant and leads to an exponential increase in temperature. The need to protect the processor from overheating will require sacrificing part of its performance.

In addition, the reduction in area also presents a number of practical engineering issues. For example, the vertical bonding of silicon wafers using technologies like Die Stacking requires pads and slots in silicon (TSVs), the size of which cannot be reduced as easily. In addition, the I / O connection areas also do not scale at the speed of Moore's Law.

3-D integration and TSV in pictures :)

As a result: the area of microprocessors will decrease further, most likely it will not (and if it does, it will be very slow). But if earlier the additional transistors brought by each new generation of the process technology were used to increase productivity (about 1.4 times for each generation), now they are used to reduce energy consumption (by about 40% for each generation)

To be continued .

Sources

- Gordon Moore (1965). "Cramming more components onto integrated circuits"

- Mark Bohr, Intel, 2011

- Shekhar Borkar, Intel, 2010

- Mark Bohr, (2007) “A 30 Year Retrospective on Dennard's MOSFET Scaling Paper”

- Fred Pollack, (1999) “New Microarchitecture Challenges in the Coming Generations of CMOS Process Technologies”, keynote at Micro

- Ganesh Venkatesh et al, (2010) “Conservation Cores: Reducing the Energy of Mature Computations”, ASPLOS 2010

- Michael Taylor, (2012) Is Dark Silicon Useful? Harnessing the Four Horsemen of the Coming Dark Silicon Apocalypse ", DAC 2012

- Ian Young, Intel, 2012

- Anantha Chandrakasan et al, (1992) “Low-Power CMOS Digital Design”

- W. Huang et al, (2008) "Many-core design from a thermal perspective." DAC 2008.