Another example of asynchronous circuit synthesis: VME bus controller

- Tutorial

I recently looked through a book (not all, only what was allowed):

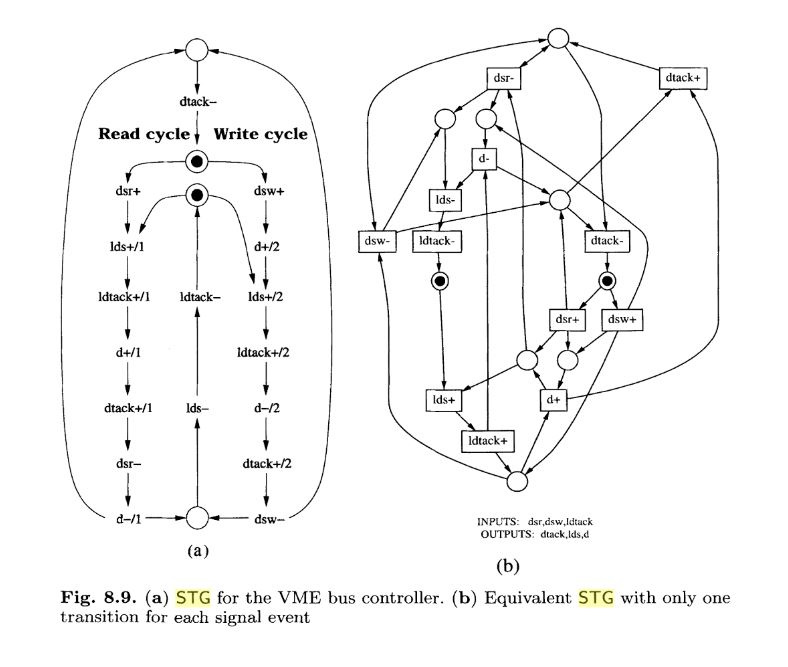

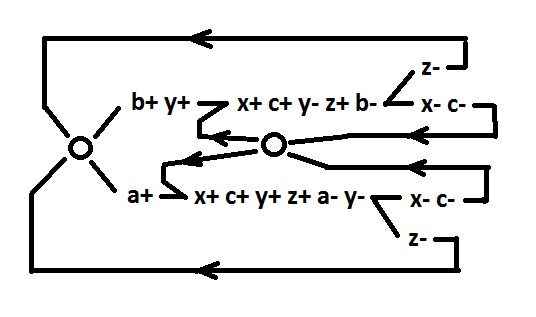

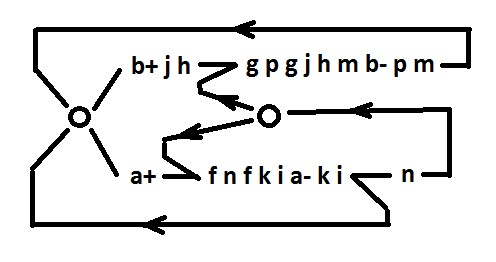

I found an example of how to make circuits using Petrify. The initial task looks like this:

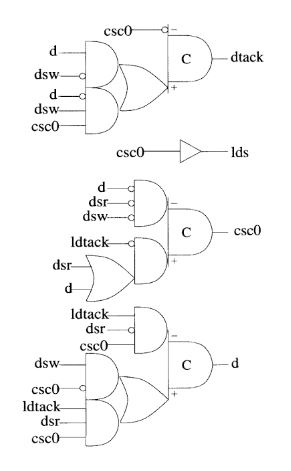

As a result, we got such an SI circuit:

Yes, we didn’t get far from Muller, well, just the C-elements were suspended. I think, nevertheless, it is necessary to show how to make asynchronous circuits. To get started, it’s better to get acquainted with this.

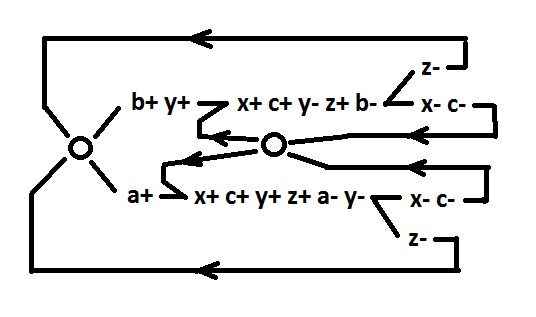

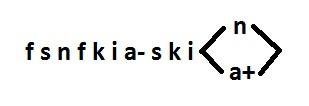

And here I will analyze the given example. To start, I’ll draw the original behavior more conveniently and replace the long signal names:

dsr - a

dsw - b

ldtack - c

lds - x

d - y

dtack - z

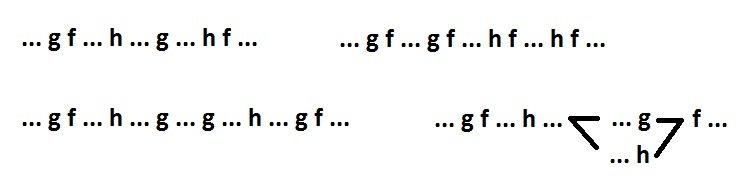

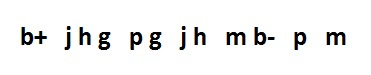

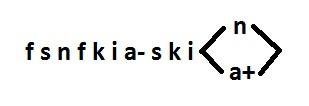

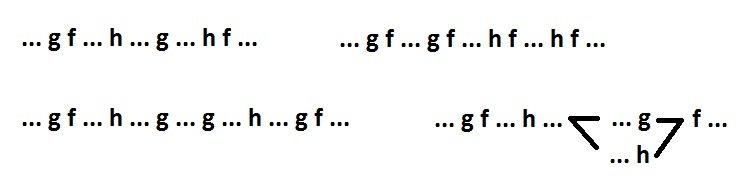

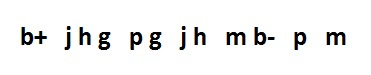

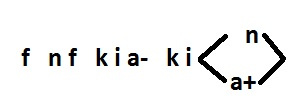

To synthesize an SI circuit on two-input elements, it is necessary to supplement the initial behavior with new signals so that each non-input signal (f) could be entered into one of the following patterns (or a combination of them):

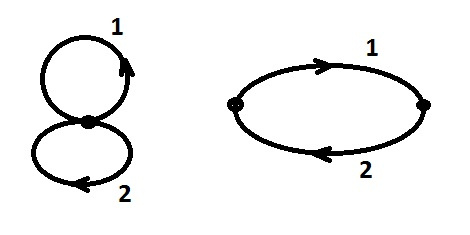

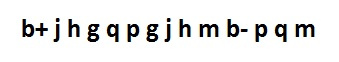

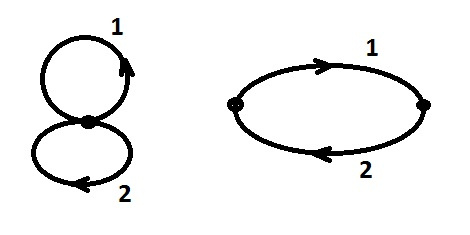

To understand how to use patterns in relation to the behavior with the choice , consider a behavior consisting of two alternative branches. And then consider the behavior of the same two branches, but arranged sequentially one after another.

It is easy to verify that the logical functions for both of these behaviors are the same. This is understandable, the second behavior is the same as the first, only with a fixed discipline of switching input signals. Accordingly, in order to use the template in relation to the behavior with a choice, you need to sequentially at least once go through all the branches in an arbitrary order (but only one that allows the original task). And one more note: additional signals will be inserted without fixing the sign. Signs will be placed at the very end.

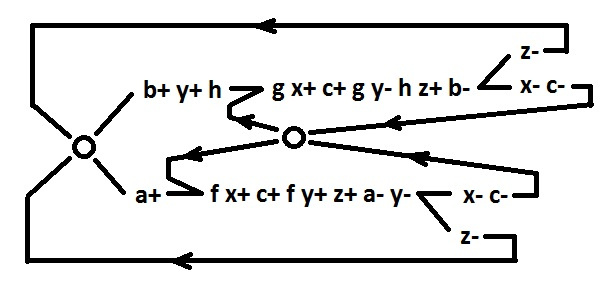

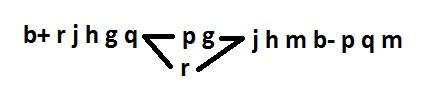

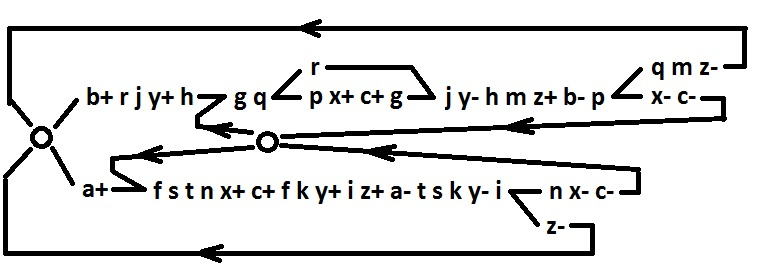

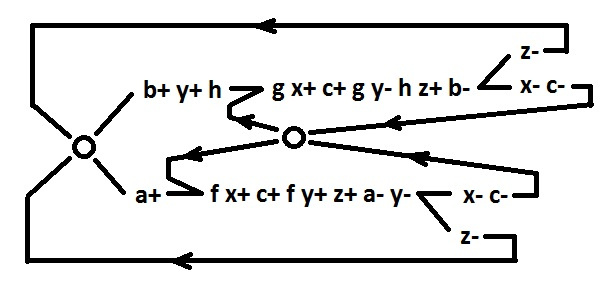

So, let's look at the original behavior. The problem that needs to be solved first: the choice occurs simultaneously with the parallel branch x- c-. It is necessary to synchronize this branch. Bearing in mind the further fragmentation of behavior, it is better to synchronize separately for each alternative branch. and at the same time isolate the signal c.

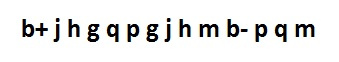

The added signal f fits into the template (i.e., has a two-input implementation) using the existing signals (f = ac). Signal g could be entered into the pattern using signals y and c, but it is better to add signal h, which can later be used to isolate signal y. The signals f, g are declared pseudo input, i.e. we forbid to put new signals in front of them (so as not to spoil the two-input implementation).

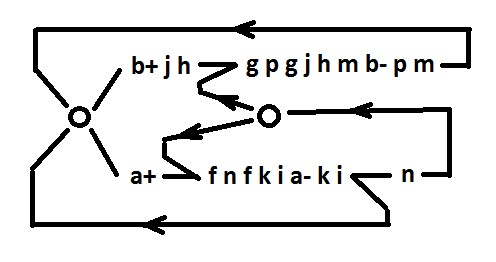

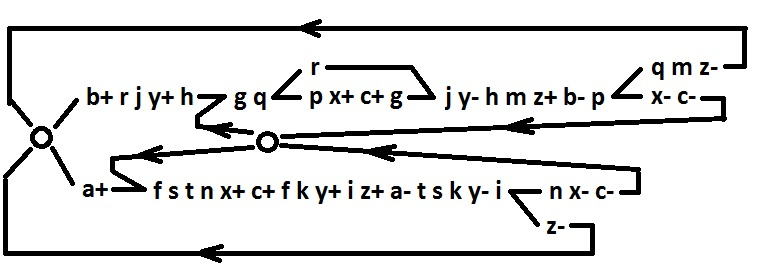

The investigated behavior is clearly divided into two alternative branches. Therefore, it can be divided into two independent behaviors, each of which will be one of the alternative branches. To do this, isolate the signals found in both branches. To isolate the signal x means to obtain a two-input implementation (fit into the template) for this signal x and for all the consequence signals (signals whose switching is the result of switching the signal x). Thus, we eliminate the influence of the signal x on the circuit and then we may not consider it.

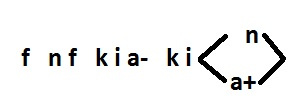

Common for both branches are signals - c, x, y, z. The signal c is input, it does not require implementation. Its consequences f, g are already realized. The consequences of signals x and z are input signals; implementation is not required for them. For the consequences of the signal y, we use h and the new signal i (h = yb, i = yb). Signals h and i are now pseudo inputs. To implement the signal y, insert new j and k (y = jk). The signal z is realized using the existing signal i and the new signal m (z = im). To realize the signal x, we add new signals n and p (x = np). Signals y, z, x are now pseudo inputs.

We remove the isolated signals from the graph. The actions are the same as when adding a signal, only the reverse sequence. The reason for removing signals is as follows: to synthesize a circuit for behavior with isolated signals, it is enough to build a circuit for the same behavior, but with remote isolated signals.

Signals a, b are input, f, g, h, i are pseudo input.

To synthesize a circuit for this behavior (with unique signals in each branch), it is enough to synthesize two circuits for each alternative branch separately. The fact that the branch n is parallel to the choice point is not an obstacle, because this branch is synchronized by the pseudo-input signal g.

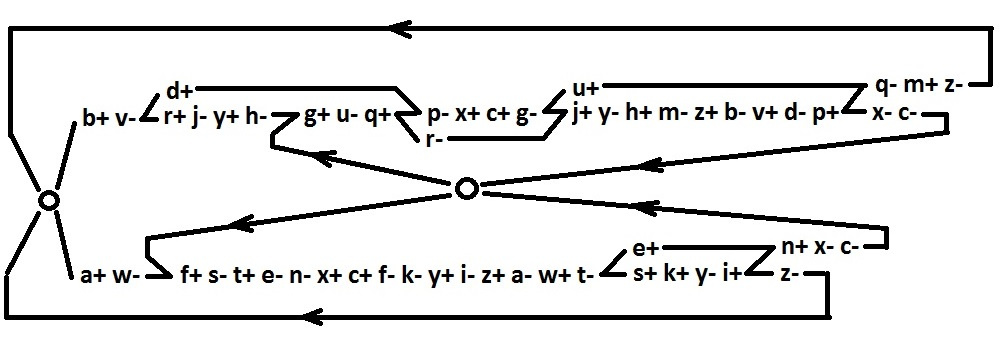

Consider separately the upper branch.

Signals b, g, h are input or pseudo input.

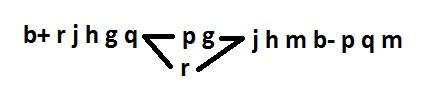

Consider readiness for decomposition. There are no CSC violations. Signal m already has a two-input implementation (m = ph). For signal j, the signal g can be used as dual. For signal p, add the dual signal q.

Now we find the logical functions. While the signs are not arranged, the form of the function is conditional.

m = qh

p = bq

q = gp

j = g + bp or j = g + bq

We decompose j (thereby introduce a new signal r).

j = rg

r = bp or r = bq

Remember that r can be a consequence of p (instead of - q). This can come in handy when arranging characters.

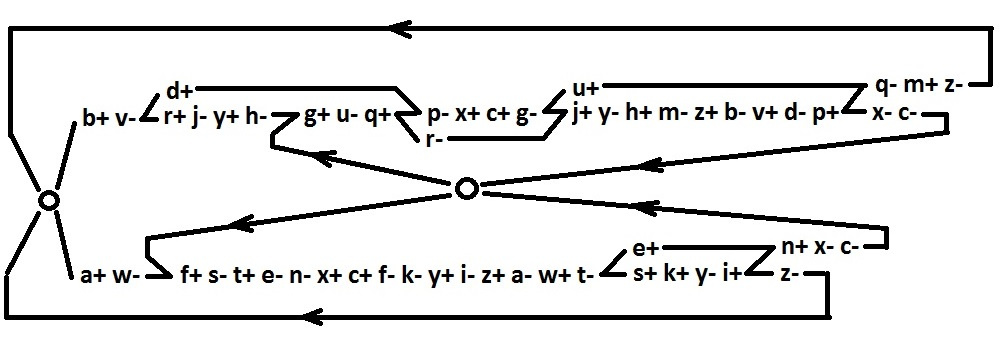

Now consider separately the lower branch.

Signals a, f, i are input or pseudo input.

There are CSC violations. These are the sequences: nfnf and ki a- ki a +. It is eliminated in the only possible way (signal s).

The signals n, k already have a two-input implementation (n = si, k = fs). For signal s, the dual signal t is required.

Now the logical functions look like this:

n = ti

r = fs

s = ft

t = as

For both alternative branches all signals are reduced to realizability in a two-input basis. Now we will restore the behavior in full, with all the added signals.

And finally, let's place the signs. The resulting mismatch of inputs for signals i, f, q, p, n is corrected by adding inverters v, w, u, d, e, respectively.

And here are the logical functions for all signals.

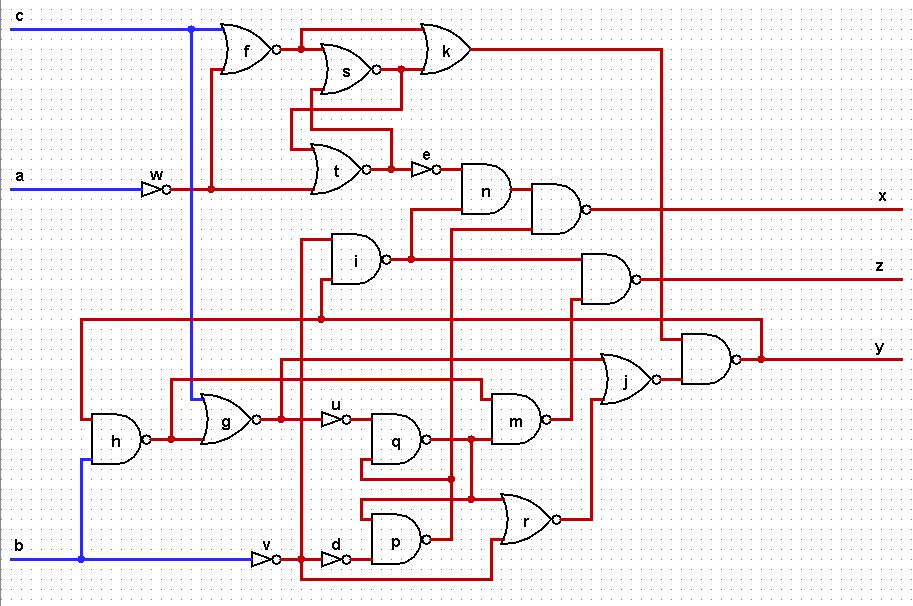

The circuit looks like this:

Counted transistor pairs. Deafening superiority did not work. 78 to 94, if not mistaken. Anyway. I tried in vain, or something. I publish.

I found an example of how to make circuits using Petrify. The initial task looks like this:

As a result, we got such an SI circuit:

Yes, we didn’t get far from Muller, well, just the C-elements were suspended. I think, nevertheless, it is necessary to show how to make asynchronous circuits. To get started, it’s better to get acquainted with this.

And here I will analyze the given example. To start, I’ll draw the original behavior more conveniently and replace the long signal names:

dsr - a

dsw - b

ldtack - c

lds - x

d - y

dtack - z

To synthesize an SI circuit on two-input elements, it is necessary to supplement the initial behavior with new signals so that each non-input signal (f) could be entered into one of the following patterns (or a combination of them):

To understand how to use patterns in relation to the behavior with the choice , consider a behavior consisting of two alternative branches. And then consider the behavior of the same two branches, but arranged sequentially one after another.

It is easy to verify that the logical functions for both of these behaviors are the same. This is understandable, the second behavior is the same as the first, only with a fixed discipline of switching input signals. Accordingly, in order to use the template in relation to the behavior with a choice, you need to sequentially at least once go through all the branches in an arbitrary order (but only one that allows the original task). And one more note: additional signals will be inserted without fixing the sign. Signs will be placed at the very end.

So, let's look at the original behavior. The problem that needs to be solved first: the choice occurs simultaneously with the parallel branch x- c-. It is necessary to synchronize this branch. Bearing in mind the further fragmentation of behavior, it is better to synchronize separately for each alternative branch. and at the same time isolate the signal c.

The added signal f fits into the template (i.e., has a two-input implementation) using the existing signals (f = ac). Signal g could be entered into the pattern using signals y and c, but it is better to add signal h, which can later be used to isolate signal y. The signals f, g are declared pseudo input, i.e. we forbid to put new signals in front of them (so as not to spoil the two-input implementation).

The investigated behavior is clearly divided into two alternative branches. Therefore, it can be divided into two independent behaviors, each of which will be one of the alternative branches. To do this, isolate the signals found in both branches. To isolate the signal x means to obtain a two-input implementation (fit into the template) for this signal x and for all the consequence signals (signals whose switching is the result of switching the signal x). Thus, we eliminate the influence of the signal x on the circuit and then we may not consider it.

Common for both branches are signals - c, x, y, z. The signal c is input, it does not require implementation. Its consequences f, g are already realized. The consequences of signals x and z are input signals; implementation is not required for them. For the consequences of the signal y, we use h and the new signal i (h = yb, i = yb). Signals h and i are now pseudo inputs. To implement the signal y, insert new j and k (y = jk). The signal z is realized using the existing signal i and the new signal m (z = im). To realize the signal x, we add new signals n and p (x = np). Signals y, z, x are now pseudo inputs.

We remove the isolated signals from the graph. The actions are the same as when adding a signal, only the reverse sequence. The reason for removing signals is as follows: to synthesize a circuit for behavior with isolated signals, it is enough to build a circuit for the same behavior, but with remote isolated signals.

Signals a, b are input, f, g, h, i are pseudo input.

To synthesize a circuit for this behavior (with unique signals in each branch), it is enough to synthesize two circuits for each alternative branch separately. The fact that the branch n is parallel to the choice point is not an obstacle, because this branch is synchronized by the pseudo-input signal g.

Consider separately the upper branch.

Signals b, g, h are input or pseudo input.

Consider readiness for decomposition. There are no CSC violations. Signal m already has a two-input implementation (m = ph). For signal j, the signal g can be used as dual. For signal p, add the dual signal q.

Now we find the logical functions. While the signs are not arranged, the form of the function is conditional.

m = qh

p = bq

q = gp

j = g + bp or j = g + bq

We decompose j (thereby introduce a new signal r).

j = rg

r = bp or r = bq

Remember that r can be a consequence of p (instead of - q). This can come in handy when arranging characters.

Now consider separately the lower branch.

Signals a, f, i are input or pseudo input.

There are CSC violations. These are the sequences: nfnf and ki a- ki a +. It is eliminated in the only possible way (signal s).

The signals n, k already have a two-input implementation (n = si, k = fs). For signal s, the dual signal t is required.

Now the logical functions look like this:

n = ti

r = fs

s = ft

t = as

For both alternative branches all signals are reduced to realizability in a two-input basis. Now we will restore the behavior in full, with all the added signals.

And finally, let's place the signs. The resulting mismatch of inputs for signals i, f, q, p, n is corrected by adding inverters v, w, u, d, e, respectively.

And here are the logical functions for all signals.

The circuit looks like this:

Counted transistor pairs. Deafening superiority did not work. 78 to 94, if not mistaken. Anyway. I tried in vain, or something. I publish.