Java Multicore Programming: Lecture # 1

Good afternoon.

On May 15, the first webinar (out of 16) of the course “Multicore programming in Java” was held . Here I would like to publish the materials mentioned in the lecture: links to sources , terms , pictures , assignment . Perhaps someone will find them useful for themselves.

I also teach the Scala for Java Developers course on the online education platform udemy.com (similar to Coursera / EdX).

It is worthwhile to “see the pictures” in the following sources

Maurice Herlihy, Nir Shavit, “The Art of Multiprocessor Programming” : “Hardware Basics” page 469-482

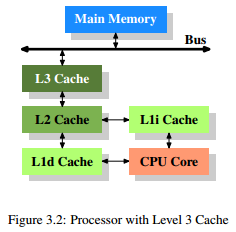

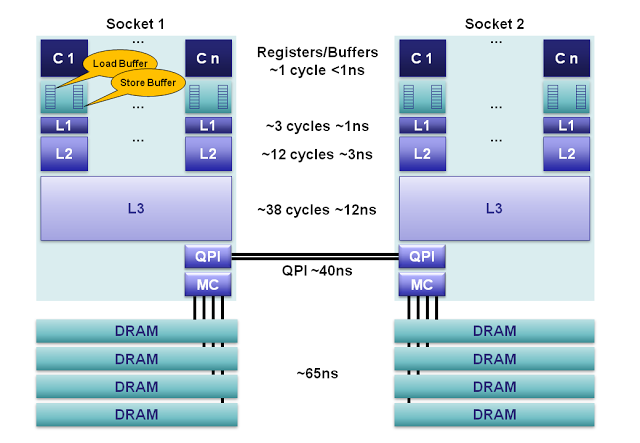

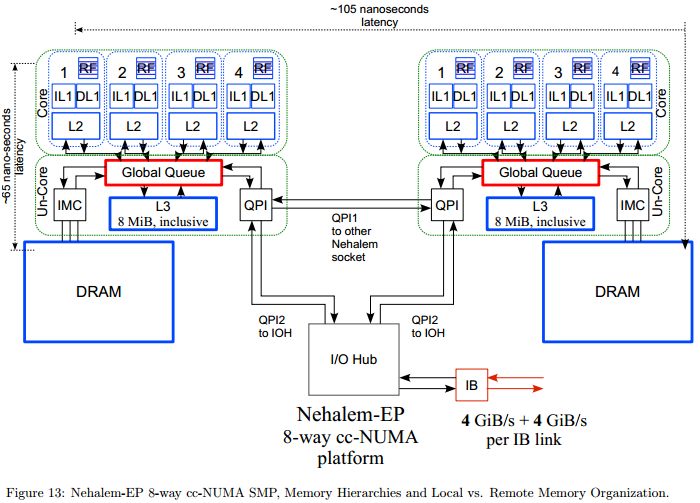

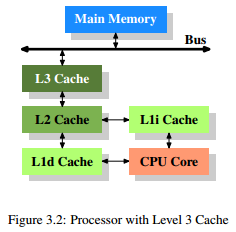

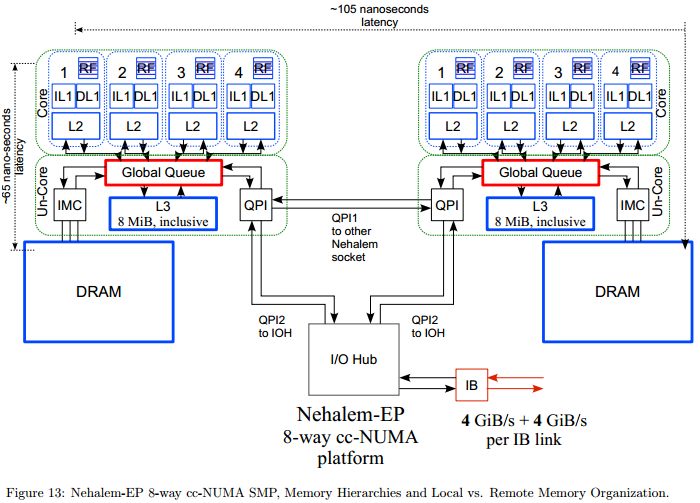

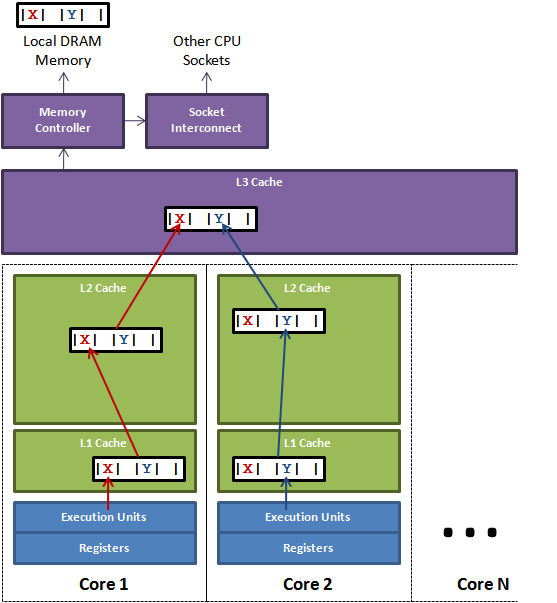

Memory hierarchy # 1

Memory hierarchy # 2

Memory hierarchy # 3

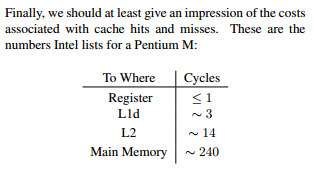

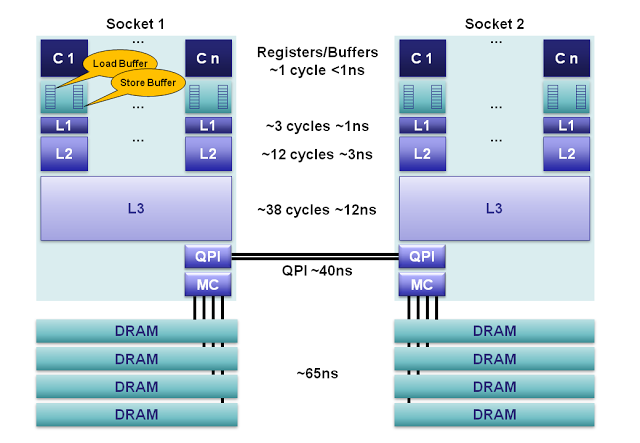

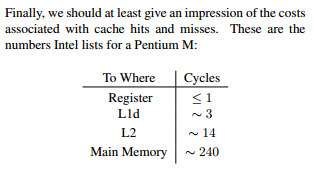

Typical access times for different memory levels

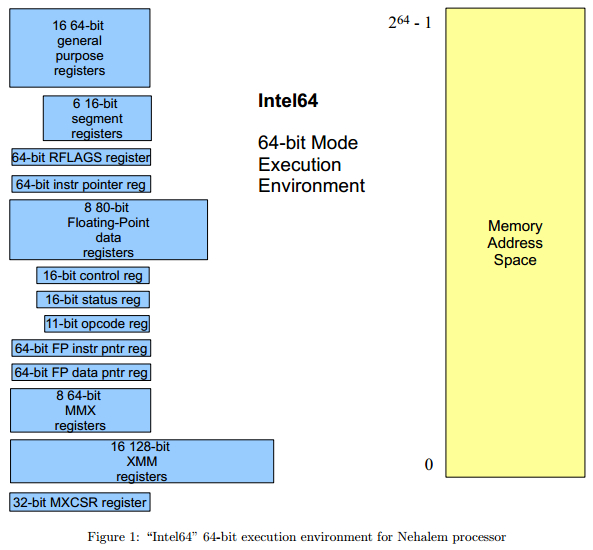

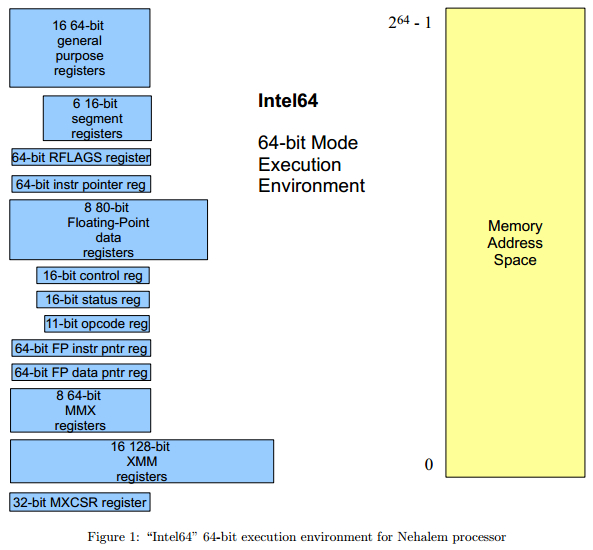

Examples of specific processor registers

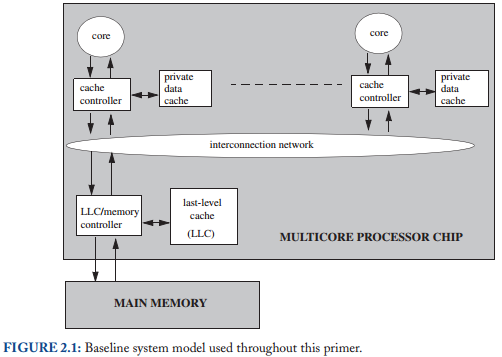

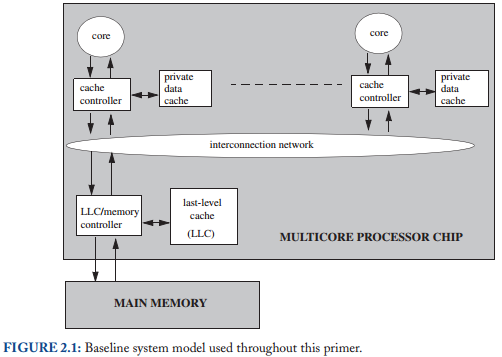

Schematic interaction of cache controllers

False sharing: code

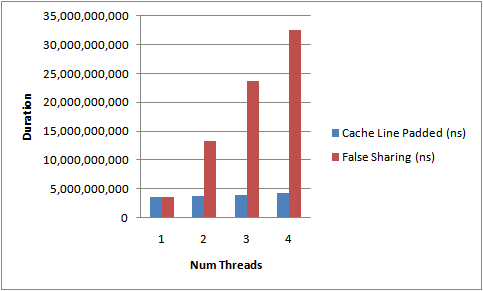

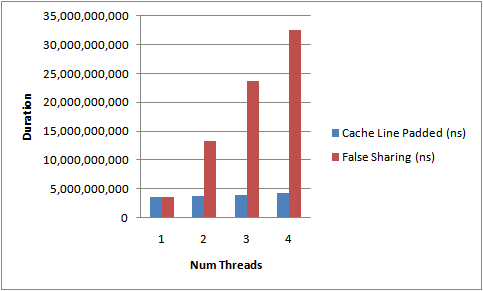

False sharing: effect (negative scalability)

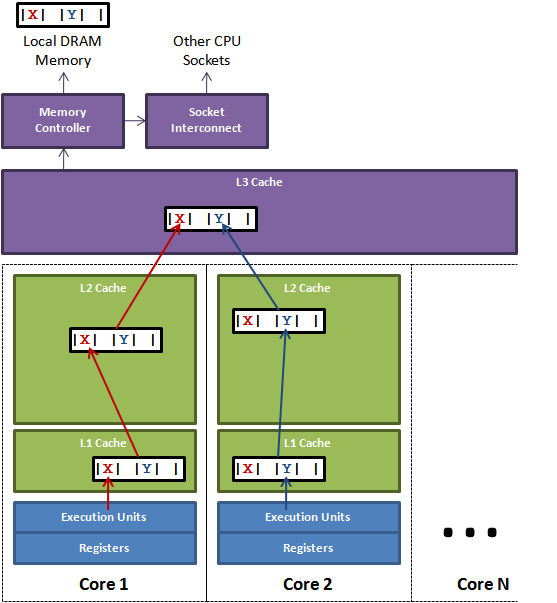

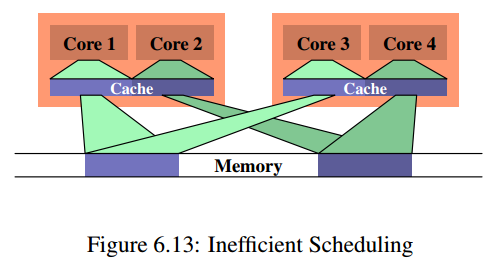

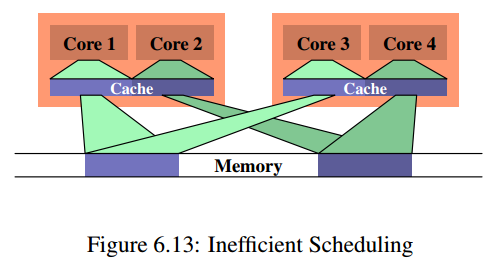

Poor match between cores, caches and data

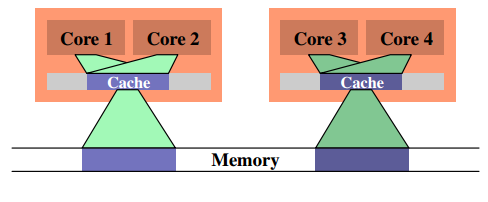

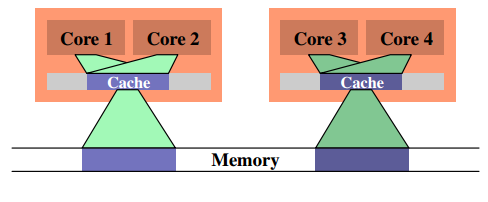

Good match between cores, caches and data

Terms

CPU, core, multicore era, memory wall, memory hierarchy, registers, L1 / L2 / L3 caches, cache line, false sharing, memory padding, cache pollution, cache miss, SMP, NUMA, multisocket, thread affinity

What to read in terms

- Mechanical Sympathy: “CPU Cache Flushing Fallacy”

- Mechanical Sympathy: “Memory Access Patterns Are Important”

- Mechanical Sympathy: “False Sharing”

- Mechanical Sympathy: “False Sharing && Java 7”

- Ruslan Cheremin: “False sharing”

- Ruslan Cheremin: “Cache coherency # 3: false sharing”

- Ruslan Cheremin: “How caching affects hashing”

Write a utility class (in option A or in both options (A and B)) that returns the following processor characteristics

- cache line size

- number and size of caches (L1, L2, L3)

- number of cores

- defines SMP or NUMA architecture

A ) by "setting up software experiments." It is recommended to read the article “Gallery of Processor Cache Effects” (in lecture # 2 we will analyze examples from the article and outline ways to solve the problem)

B) by using JNA to call the operating system API

Webinars, video in recordings, source code of programs and verification of tasks are available only to those who register for the course.

I do Java training online (here are the programming courses ) and publish part of the training materials as part of the redesign of the Java Core course . You can see video recordings of lectures in the audience on the youtube channel , perhaps the video of the channel is better systematized in this article .

skype: GolovachCourses

email: GolovachCourses@gmail.com

On May 15, the first webinar (out of 16) of the course “Multicore programming in Java” was held . Here I would like to publish the materials mentioned in the lecture: links to sources , terms , pictures , assignment . Perhaps someone will find them useful for themselves.

I also teach the Scala for Java Developers course on the online education platform udemy.com (similar to Coursera / EdX).

Introduction

- Moore's Law, Moore's law

- Herb Satter, “The Free Lunch Is Over”

- Amdahl's Law, Amdahl's law

"Iron"

It is worthwhile to “see the pictures” in the following sources

- "What Every Programmer Should Know About Memory"

- "The Architecture of the Nehalem Processor and Nehalem-EP SMP Platforms"

- “A Primer on Memory Consistency and Cache Coherence”

Textbooks

Maurice Herlihy, Nir Shavit, “The Art of Multiprocessor Programming” : “Hardware Basics” page 469-482

"Images"

Memory hierarchy # 1

Memory hierarchy # 2

Memory hierarchy # 3

Typical access times for different memory levels

Examples of specific processor registers

Schematic interaction of cache controllers

False sharing: code

False sharing: effect (negative scalability)

Poor match between cores, caches and data

Good match between cores, caches and data

Terms

Terms

CPU, core, multicore era, memory wall, memory hierarchy, registers, L1 / L2 / L3 caches, cache line, false sharing, memory padding, cache pollution, cache miss, SMP, NUMA, multisocket, thread affinity

What to read in terms

- Mechanical Sympathy: “CPU Cache Flushing Fallacy”

- Mechanical Sympathy: “Memory Access Patterns Are Important”

- Mechanical Sympathy: “False Sharing”

- Mechanical Sympathy: “False Sharing && Java 7”

- Ruslan Cheremin: “False sharing”

- Ruslan Cheremin: “Cache coherency # 3: false sharing”

- Ruslan Cheremin: “How caching affects hashing”

Assignment to Lecture # 1

Write a utility class (in option A or in both options (A and B)) that returns the following processor characteristics

- cache line size

- number and size of caches (L1, L2, L3)

- number of cores

- defines SMP or NUMA architecture

A ) by "setting up software experiments." It is recommended to read the article “Gallery of Processor Cache Effects” (in lecture # 2 we will analyze examples from the article and outline ways to solve the problem)

B) by using JNA to call the operating system API

public class HardwareSpy {

public int cacheLineSize() {...}

public int cacheL1Size() {...} // -1 если считается, что нет L1

public int cacheL2Size() {...} // -1 если считается, что нет L2

public int cacheL3Size() {...} // -1 если считается, что нет L3

public int coreCount() {...}

public int isSMP() {...}

public int isNUMA() {...}

}

Contacts

Webinars, video in recordings, source code of programs and verification of tasks are available only to those who register for the course.

I do Java training online (here are the programming courses ) and publish part of the training materials as part of the redesign of the Java Core course . You can see video recordings of lectures in the audience on the youtube channel , perhaps the video of the channel is better systematized in this article .

skype: GolovachCourses

email: GolovachCourses@gmail.com