The Las Vegas exhibition is for electronics developers, not consumers. A report from Design Automation Conference

I decided to write this note on Habré in Russian and in English in order to distribute a link to it both in English and Russian-language forums and groups. The Russian text is not a translation of English and vice versa - I just wrote a note twice (I hate translating). Those who want to criticize my English are immediately sent to the end of the post, where they will be shocked by my accent in a long hours-long video. I see my emphasis not as a bug, but as a feature. We all know that many Americans find, for example, a nasopharyngeal British accent attractive. It is time to give the same status to a severe Russian accent. To do this, as many Russians as possible need to make speeches at various international events. Our password is “years mi Speak From May Hart”.

But first about the exhibition.

Millions of gadget consumers around the world are watching the Consumer Electronics Show (CES), which is taking place in Las Vegas in January. They, who never knew what a D-trigger is, importantly argue that four gigahertz is better than three in the latest processors from AMD and Qualcomm. But there is an exhibition focused not on consumers, but on electronics developers. This exhibition is called the Design Automation Conference (DAC), and in some years it also takes place in Las Vegas, but not in December, but in June.

Millions of gadget lovers every year watch the Consumer Electronics Show (CES) which takes place in Las Vegas in January. Those folks, who never learned the function of a D-flip-flop and how the static timing is calculated, discuss gigahertz frequencies after reading the latest articles in Wired magazine they perceive as a technical publication. However there is another conference, not for the consumers, but for the creators of electronics. This conference is called the Design Automation Conference (DAC) and it also takes place in Las Vegas, although not every year, and not in January, but in June.

The industry of Electronic Design Automation (EDA) makes software for hardware designers. EDA is controlled by three large companies: Synopsys, Cadence and Mentor Graphics (now a part of Siemens). Both Synopsys and Cadence have a complete set of products, necessary to design and simulate a digital chip on multiple levels. The design flow, called RTL2GDSII, starts from specification and coding the circuit's cycle behavior in hardware description language (Verilog or VHDL), proceeds with synthesizing this description into a graph of logic elements (netlist), then continues to placing the netlist into a physical blueprint of the chip and routing on-chip wires to connect the standard cells, the building blocks of ASICs (Application-Specific Integrated Circuits).

Three large companies dominate the electronics design automation industry: Synopsys, Cadence and Mentor Graphics (which Siemens bought a couple of years ago). Synopsys and Cadence have created a software that covers the entire RTL2GDSII design route. I briefly described this route in my previous DAC article four years ago:

Over the past25 to30 years, the design of the microcircuit is most often written in the language of equipment description Verilog (in Europe and the military - VHDL), after which a special program (logic synthesis) turns the design into a graph of wires and logical primitives, another program (static timing analysis) tells the designer whether it fits into the speed budget, and the third program (place-and-route) lays out this design on the site of the chip.

When the design goes through all the stages: coding on a veril, debugging, verification, synthesis, static timing analysis, floorplanning, place-n-route, parasitics extraction, etc. - it turns out a file called GDSII, which is sent to the factory, and the factory bakes chips. The most famous factories of this type are owned by Taiwan Semiconductor Manufacturing Company or TSMC.

John Sanguinetti, a Verilog guru since 1980s. John was a founder of a company called Chronologic Simulation which, back in 1990s, created VCS, a Verilog Compiled code Simulator. This simulator is now a property of Synopsys. VCS is used by a majority of large electronic companies. VCS brought to Synopsys billion dollars in revenue.

Along the side of the showroom is John Sanguinetti, an early verilogue guru from the 1980s and founder of Chronologic Simulation. This company gave the world the fast Verilog Compiled code Simulator (VCS) simulator, which is now the property of Synopsys. This simulator is used by most major chip developers. VCS brings Synopsys billions of dollars:

Mentor Graphics is now a part of Siemens, the third-largest EDA company. Unlike Synopsys and Cadence, Mentor Graphics does not have a full line of RTL2GDSII tools. Its two most recognized streams of revenue come from Caliber, a set of physical design verification tools, and Veloce, a hardware emulator. Caliber includes for example a tool that checks geometric design rules (width, spacing, enclosure) on the final "blueprints" of the chip. Veloce uses FPGA-like chips that

Mentor Graphics, the third largest company in the EDA industry, at the end of 2016 became part of Siemens. Unlike Synopsis and Keydens, Mentor does not have the entire chain of programs that cover the RTL2GDSII route. Mentor’s two major sources of income are the Caliber software package, which does checks at the final stage of chip design, and the Veloce emulator (pronounced Velochi). An example of verification in Caliber is the minimum distance between the tracks on the chip

UPD: corrected on the basis of the comment of amartology : The antenna is generally about another. It occurs when one track becomes so large that it begins to work like an antenna, receiving a signal at the frequency of plasma oscillations for etching during production.

And the Veloce emulator uses FPGA-shaped ASICs to quickly

In addition to highly profitable Caliber and Veloce projects, Mentor always had a large number of other projects, products, services, trainings and educational programs. For example Mentor is cultivating the field of functional verification, a critically important part of the digital design workflow.

In addition to highly profitable projects such as Caliber and Veloce, Mentor has many other projects, products, services, research projects and educational programs. For example, at Mentor, they are engaged in functional verification, a critical part of the production process:

A number of small companies, including Doulos, Willamette HDL and Sunburst Design, sell hardware verification training to large and medium-size electronic companies. Such niche exists because universities do not teach the art of functional verification properly and do not adopt new technologies, such as System Verilog, UVM, formal verification using concurrent assertions, Portable Stimulus, etc in their curriculum for decades. Even Stanford does not have it in their curriculum as far as I know from talking with their graduates.

Functional verification feeds several small companies that sell SystemVerilog and UVM trainings to large corporations at refreshingly high prices, such as a couple of thousand dollars per person. These include Doulos, Willamette HDL, Sunburst Design and others:

Another small company called Verific. They have just a handful of people but they are very successful in their niche. Verific sells SystemVerilog parsers adopted by important EDA companies, both large and small.

Here is another small, only a few people, but very successful company of its kind called Verific. She sells the Verilog parser, which many EDA companies use:

The founder of Verific gives an interview to a popular EDA website called EDA Cafe. There are several other popular EDA websites including John Cooley's deepchip.com but I did not meet John Cooley on DAC floor this time.

Here is Verific founder giving an interview to the EDA Cafe website, popular in the industry:

Now let's talk about FPGA.

Now let's talk about FPGAs, they are PPVM (they will correct me now), they are FPGA.

What it is, I also briefly described in my previous DAC article four years ago:

In the simplest version, an FPGA consists of a matrix of homogeneous cells, each of which can be changed into function using multiplexers connected to the bits of the configuration memory. One cell can become an AND gate with four inputs and one output, another - a single-bit register, etc. We load a sequence of bits from the memory into the configuration memory - and the given electronic circuit is formed in the FPGA, which can be a processor, display controller, etc.Two largest producers of FPGA are Xilinx and Altera, now a part of Intel.

FPGAs / FPGAs are not processors; by “programming” FPGAs (filling the configuration memory of FPGAs) you create an electronic circuit (hardware), while when programming a processor (fixed hardware) you slip a chain of sequential program instructions written into it (software).

The two largest companies that produce FPGAs are Xilinx and Altera, now part of Intel:

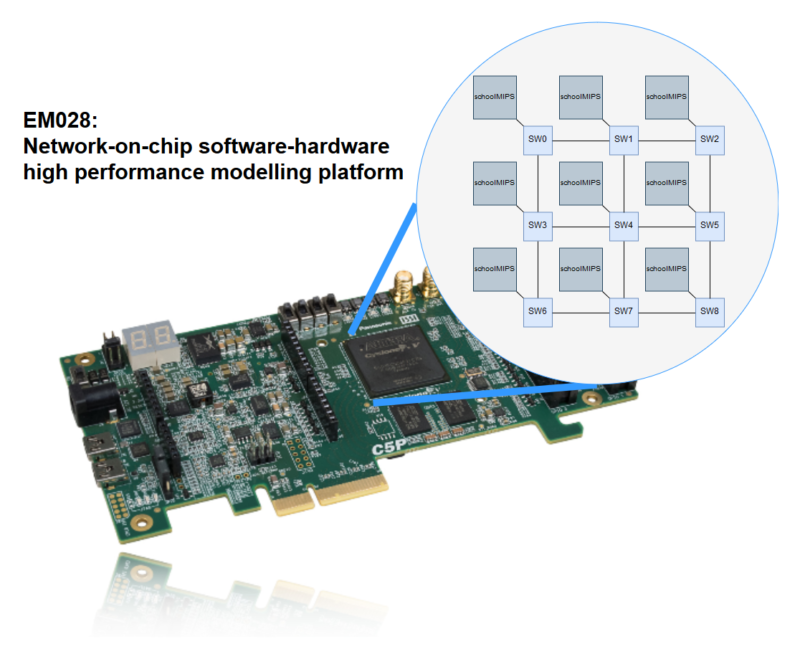

These week Intel collects votes for the first round of Innovate FPGA contest. One of Russian entries uses a mesh of tiny schoolMIPS processor cores. schoolMIPS implements a subset of MIPS architecture. It exists in several variants, including single -cycle with no data memory (the simplest one), a version with interrupts, a pipelined version, etc:

By the way, this week Intel shall vote on the Innovate FPGA competition, which involves including and Russian teams . One project is a NoC-based multiprocessing system prototype. This is a prototype network on a chip with a large number of nodes based on processors by Stanislav Zhelnio sparf (based on Harris & Harris's book “Digital Synthesis and Computer Architecture”) https://github.com/MIPSfpga/schoolMIPS . Makes 4-year student at MIEM NRU HSE:

The world of FPGAs is not limited to Xilinx and Altera / Intel. There are several much smaller vendors, like Lattice and Microsemi / Actel, and even small companies that do not design the end chips themselves bit license the design of FPGA cell blocks to ASIC companies. A useful application would be to create a reconfigurable coprocessor connected to a fixed high-frequency CPU core. Another application is security: some companies wants to hide their secrets in reconfigurable logic rather then to show the layout of their fixed logic to a motivated researcher with electron microscope and a lot of time.

But there are fewer players in the FPGA world, for example, here are two companies that license the design of FPGA blocks that can be embedded in multi-run fixed circuits to give them flexibility.

Every DAC has several FPGA board vendors. Not the vendors of cheap student boards like Digilent and Terasic, that start from $ 55, but FPGA boards for ASIC prototyping that can cost $ 30,000, $ 100,000 or more.

The DAC is traditionally attended by manufacturers of FPGA boards. They do not sell cheap student cards for $ 55 dollars, but serious FPGA boards for $ 55 _ thousand dollars and more. Their client is not a student, but a severe ASIC development team that uses large boards for prototyping.

What if a researcher did some proof of concept using FPGA and now wants to manufacture his own ASIC? A typical commercial order to manufacture an ASIC usually requires the initial payment from ~ $ 300K to ~ $ 3,000,000 depending on process technology. However there are specialized companies, Europractice in Europe and MOSIS in US, that sell small quantity “shuttle” services, or multi-project wafer (MPW) services, starting with just $ 3000 for 180nm technology or just tens thousand dollars for something modern, like 28nm.

But what if a student or a harsh company wanted to make a real ASIC in a factory, and there is little or little money? Or, if not sorry, is it a test chip or a very small batch? To do this, in America there is a company MOSIS, and in Europe - Europractice. A few thousand dollars - and you have in your hands the chip you designed for technology such as 180 nanometers. A couple of tens of thousands - and you have in your hands your chip on more recent technology, for example 28 nanometers, like the fifth iPhone. I note that for mass commercial production the initial payment to the factory is from hundreds of thousands of dollars for old technologies to two or three million for new ones.

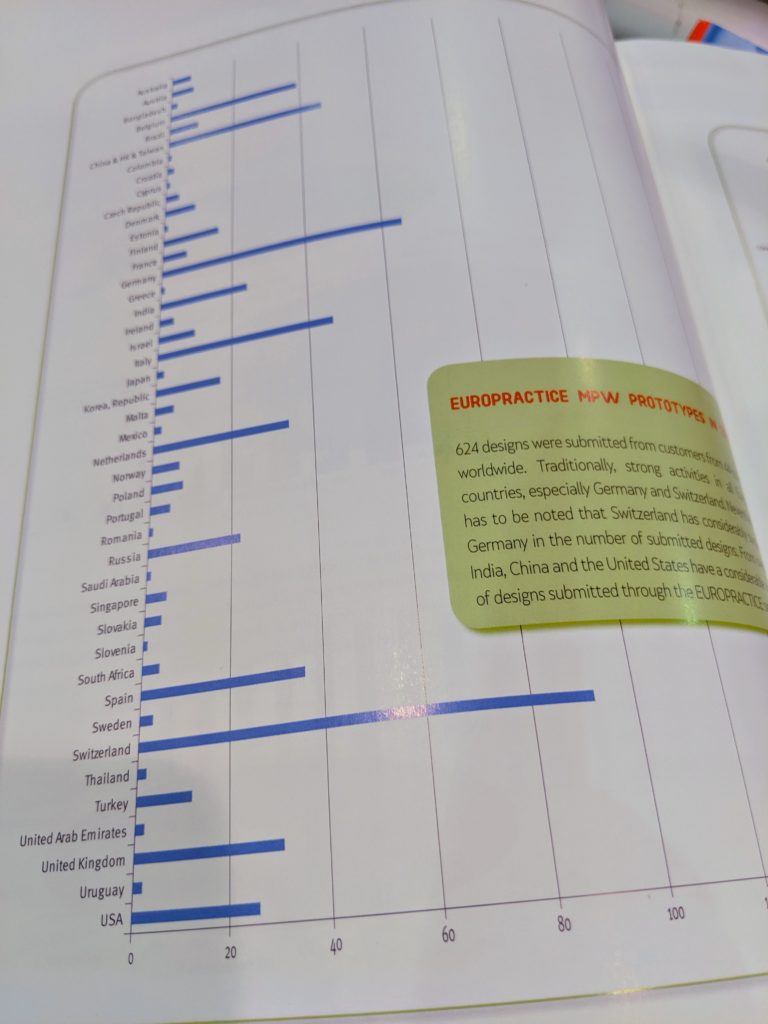

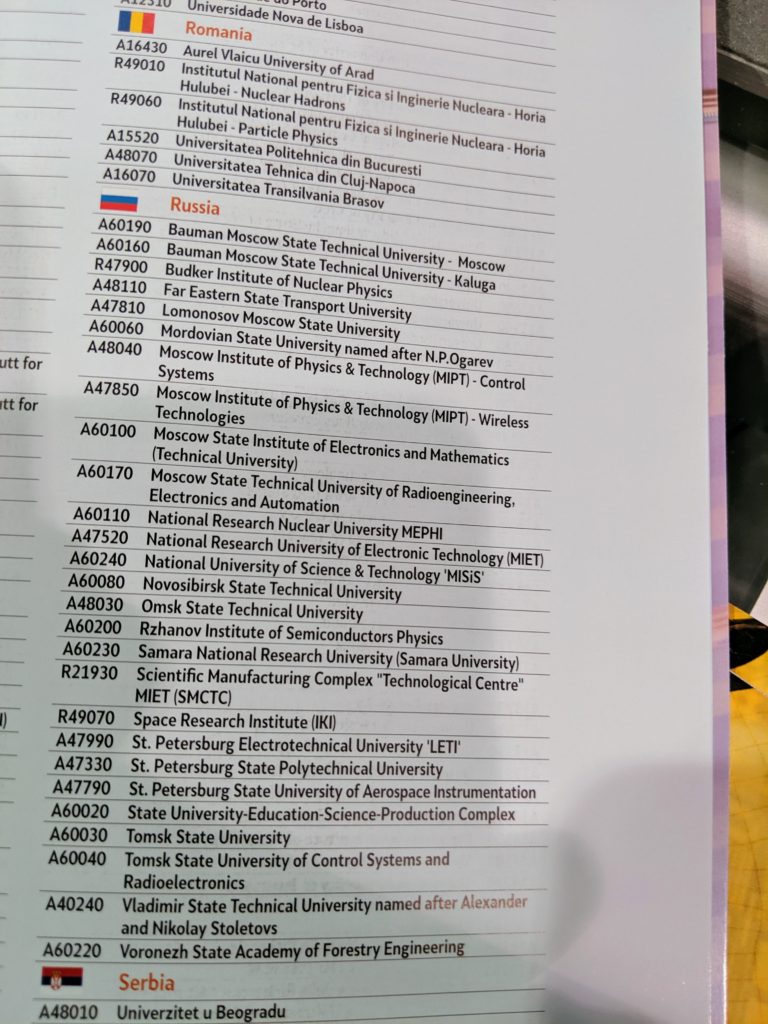

It is interesting that Europractice has customers in Russia, even in Omsk. Admit who designs the ASICs in Omsk.

Europractice has a number of Russian companies, including somebody in Omsk:

There are companies with business models that are somewhat mysterious to me. For example I don't understand how this company below can survive on a niche Eclipse plugin. I guess they get most revenue selling some consulting services.

There are companies about which I do not understand how they earn. For example, this one is selling a very niche Eclipse plugin. Surely they do not live on him, but on some kind of consulting.

Another niche company with non-obvious business model. They translate a description of software-visible registers into Verilog glue logic and other interface files. I guess this company may have some Cisco-type large customer that got hooked on their technology long time ago and pay them since then.

Another niche company with an unobvious business model. They translate the description of registers available to the programmer into verilog and interface files. They probably have some major client such as Cisco, which once many years ago fell in love with their tool, and has since been paying since it’s a bummer to hire a client to manage their engineer.

A melancholic gentleman from Huawei described their achievements in networking chips. Huawei is obviously dependent on US EDA tools, even more than on Android market and ARM CPU cores. They amount of money and the number of technical experts necessary to develop an equivalent of Synopsys IC compiler is much larger, in my opinion, than the resources needed to design a high-end competitor for ARM cores.

A representative of Huawei also sat at the exhibition with an expression of bright sadness on his face. I note that if the US government forces US EDA companies to ban the Chinese, then the Chinese situation will be much worse than it is now, since it is technically more difficult to clone Synopsys IC Compiler than ARM and Android Market processor cores.

Every DAC since 1998 had at least one company developing yet another C-to-Verilog compiler. Back in 1998 it was my own startup . This year it is somebody else:

Every 1998 DAC listing has had at least one company compiling C in Verilog. In 1998, such a company was my own startup. This year someone else:

This gentleman earns his living by selling solutions that counter so-called "Zakladki" (a Russian term, a plural of "Zakladka"). I explained to him the meaning of the term and he agreed that this is what he sells.

Here's a companion making a living with bookmark analyzers in processors:

I brought to DAC my student daughter so she can see how daddy earns living:

I brought my daughter to Las Vegas to watch how people make money in the harsh industrial world of the electronic industry, and realized that daddy’s dollars didn’t grow on trees:

Party after the exhibition:

At the party after the exhibition:

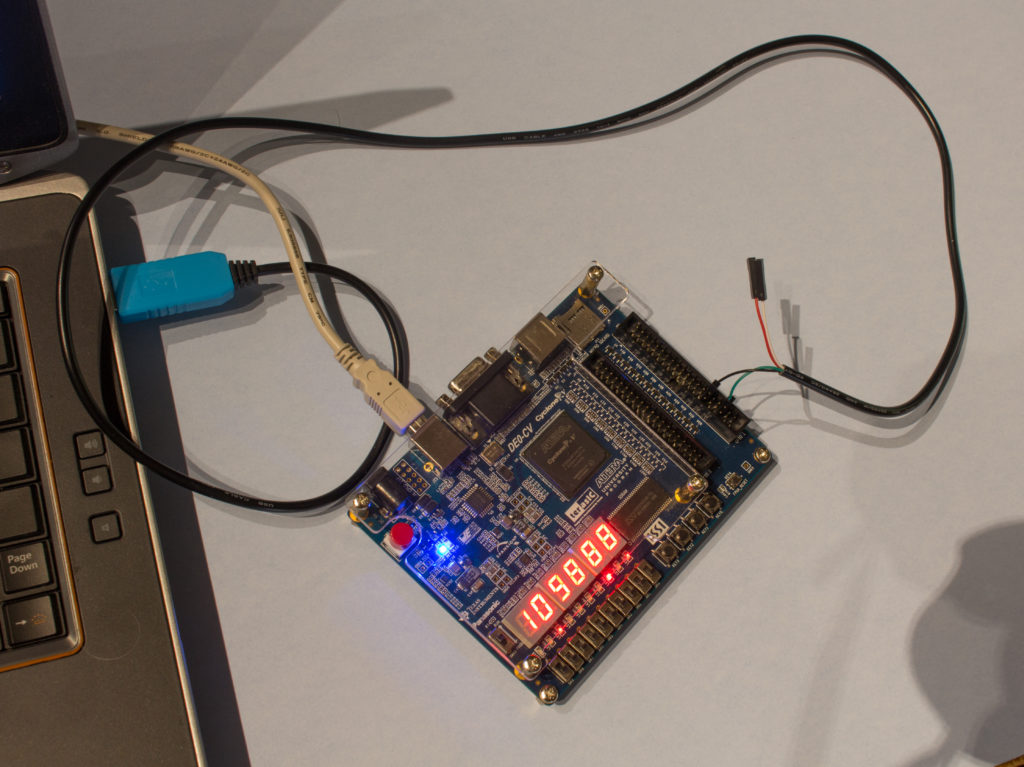

After the exhibition I did MIPS Open Developer Day together with my colleagues from Wave Comnputing. We got a number of people from some of the above companies + my Russian friends from VivEng , a California Silicon Valley mixed-signal design services that also had some customers in Zelenograd, a Russian Silicon Valley. First we made a presentation , then the participants did some exercises on Digilent Nexys4 DDR and Terasic DE10-Lite FPGA boards.

Then, together with my colleagues, I conducted the MIPS Open seminar. It was attended by comrades from some of the companies described, including those that license embedded FPGA and EDA tools, sell services for production, conduct verification training, and also make chips as such. And also my old friends from the Russian companyVivEng . My colleagues and I showed these slides , after which the participants tried examples on FPGAs Digilent Nexys4 DDR and Terasic DE10-Lite.

To repeat the results, you can download and combine the two packages:

If you want to reproduce the results, you can do the following:

- Go to https://www.mipsopen.com/mips-open-components/mips-open-fpga-getting-started-guide .

- Download the standard MIPSfpga 2.0 package.

- Go to https://github.com/MIPSfpga/mipsfpga-plus .

- git clone github.com/MIPSfpga/mipsfpga-plus.git

- Copy core RTL files from MIPS Open FPGA package to core subdirectory of MIPSfpga + package - see the instruction in https://github.com/MIPSfpga/mipsfpga-plus/tree/master/core

Either Intel FPGA Quartus Prime Lite Edition or Xilinx Vivado, as well as the Codescape GCC Bare Metal Toolchain must be installed on your computer. After that, you can follow the instructions from the slides:

You need to have Intel FPGA Quartus Prime Lite Edition or Xilinx Vivado installed on your system, as well as Codescape GCC Bare Metal Toolchain. After this you can follow the instruction from the slides:

- cd your_git_directory / boards / board_directory (for example de10_lite or nexys4_ddr)

- make all load

- Press reset (or KEY 0 on some boards) to reset the processor.

- The default hardcoded program should start to work.

- cd your_git_directory / programs / 00_counter (or other program)

- make program srecord uart

- If computer uses serial connection other than ttyUSB0 (the default), then:

- make program srecord uart UART = 1 (or 2, 3, etc)

- The program uploaded via USB-to-UART is now running.

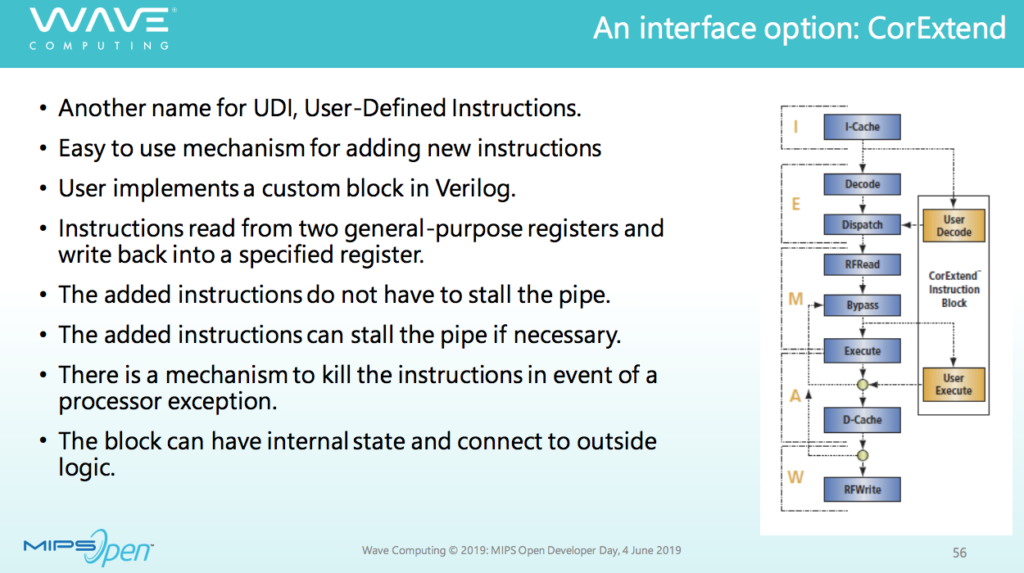

In the presentation, I showed how to embed a block in the processor that decodes and executes additional instructions to the main system of instructions that can be determined by the system designer on a chip. The block can be synthesized and become part of the microcircuit or be configured in the FPGA / FPGA.

Additional instructions move along the processor pipeline along with the main ones. They receive data from general registers visible to the programmer and can return the result to the register. These instructions can also save some state in the coprocessor. They can be killed by exceptions if an exception occurs, for example, in the pipeline following this instruction:

The presentation has a detailed explanation, how to add user-defined processors instructions to MIPS microAptiv UP CPU core and synthesize it together with some simple SoC for FPGA board:

Code fragment in the Verilog hardware description language from the sample text. This code implements, at the Register Transfer Level (RTL), a specialized instruction for computing a convolutional neural network:

A fragment of a custom CorExtend module that implements a User-Defined Instruction (UDI) for a special case of neural net computation:

Tomorrow I am flying to Russia to help with another seminar, not for electronic and EDA professionals, but for kids interested in exploring careers in digital microelectronic design. For this trip I created a simple 2D videoprocessor integrated with MIPS Open FPGA core, as well as an example of a hardware-only (no CPU or software) game for VGA. Kids like games and I am going to use game design to teach them the basics of RTL methodology:

And next Monday , July 8, I will teach the basics of developing digital circuits for schoolchildren in Zelenograd .

For him, I wrote examples of the implementation of simple sprite graphics on FPGA. A circuit synthesized from verilogue draws sprites on a VGA screen.

Here is a working example in a clean hardware ( source codes on github) A variant of naval combat, where a red torpedo satellite hunts for an enemy blue cross:

And here is an example of a combination of hardware and software - a salute from sprites. Hardware part and software part :

Yes, and I promised to give my speeches in Las Vegas. Here is a piece:

View of the Las Vegas Strip when its getting dark but there are no crowds yet:

And the view of the street on the strip, when it is already evening, but there are no crowds yet:

During two days in Las Vegas I did not get a chance to gamble, so I played with $ 1 when our plane back to San Jose was boarding in Las Vegas airport:

For all this time in Las Vegas I have not played since I went around the exhibition and talked about electronic topics, then I conducted a seminar. But while boarding the plane, I nevertheless noted, lost one dollar: