Prototyping ASIC on FPGA

Chip development is complex, expensive, and time consuming. And the price of any mistake is extremely high. After making the crystal with patches and updates, nothing can be fixed. Therefore, they are especially scrupulous in checking design schemes at the design stage. For each functional block, block tests are written in all operating and non-operating modes. After integrating the block into the general circuit, system tests are conducted on how this block works as part of the system. All tests are constantly spinning in regression testing. There is even an informal sign of a less or less acceptable level of testing - when the amount of test code is 10 times the amount of code of the unit being tested. But all these tests do not give the feeling that the circuit is viable, since any simulation is the behavior of the circuit for hundreds of milliseconds maximum. But in life, the circuit should work out hundreds of thousands of hours. I once looked for a failure when 1 or 2 bytes were lost per 1 GB of transmitted information and no functional tests found this problem. And this error was manifested only on the FPGA prototype of the future chip. About what prototypes we did and what is going on in the world, this article will tell.

Prototyping future chips on an FPGA is the only way to test how the circuit works on real-world tasks in less real-time. The prototype allows you to debug software, get initial performance characteristics, and much more. Modern FPGAs have a sufficiently large amount of resources for these tasks. For example, you yourself can implement a full-fledged computer with an Intel 8086 processor on a motherboard with FPGA for $ 300 .

Unfortunately, we could not find the very first prototype in the deposits of our cabinet with skeletons, but it was a small scarf based on the Xilinx Spartan3-400 (XC3S400). 400 means the number of thousands of valve equivalents that are available to the developer to create their circuit. The price of the handkerchief was approximately $ 50 and allowed to implement in it a simple 8-bit microcontroller with all memory and at a frequency of 40 MHz. Prototyping consisted in the fact that the developed microcontroller on it blinked an LED.

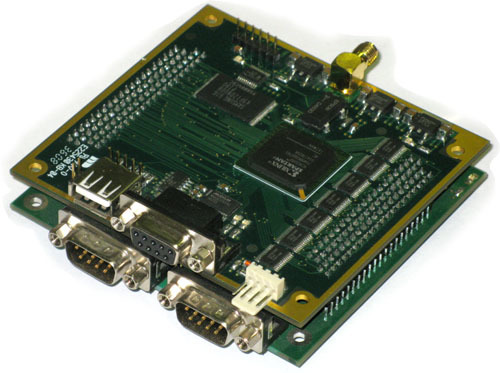

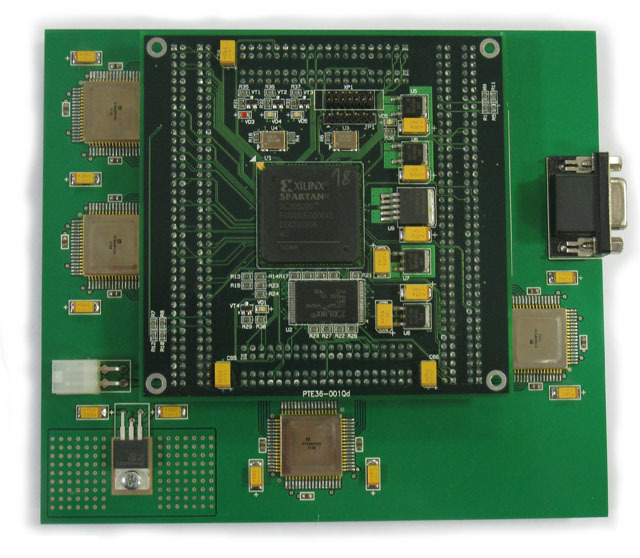

The special board for the prototype was already developed not as an experiment, but as a meaningful stage of the project. Already applied FPGA Xilinx Spartan3-1000. Those. 1 million valves were already available to us, and the designed microcontroller worked at its maximum frequency of 48 MHz. And it was on this board that I caught the very 2 lost bytes per gigabyte. The price of the board was approximately $ 200.

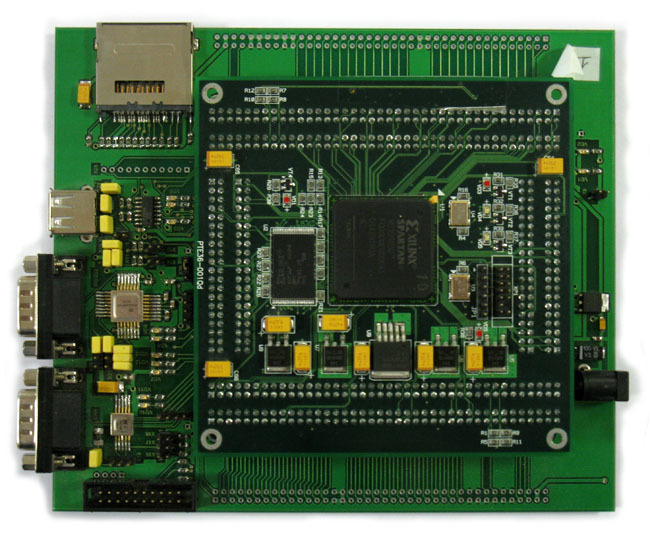

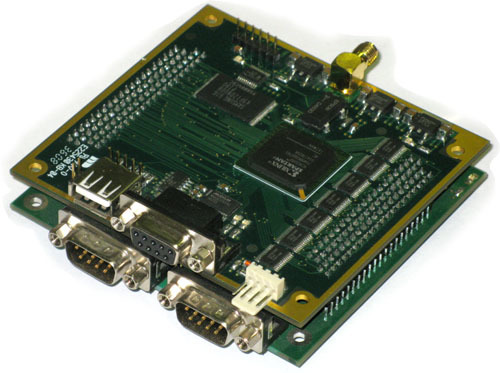

For the new 32-bit microcontroller, it was obvious that 1 million valves might not be enough. Therefore, a new motherboard based on Xilinx Spartan3-5000 was developed, thanks to which 5 million valves have already become available. The price of the board was approximately $ 500 and for a long time this board became the main one for prototyping new developments. On its basis, not only microcontrollers were tested, but also various specialized microcircuits. The designed microcontroller in FPGA was already operating at a reduced frequency of 20 MHz, although then in silicon it worked at frequencies of 100 MHz and even 150 MHz.

Prototype of a 32-bit microcontroller:

Prototype of a video card (unfortunately, the project did not go live, but the finished RTL is waiting in the wings):

Prototype of a 4-way Ethernet switch with built-in transceivers:

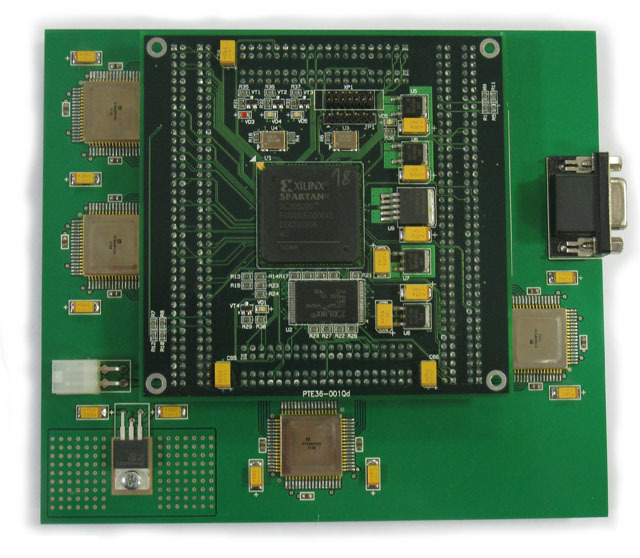

When developing a dual-core microcontroller (32-bit RISC + 16-bit DSP core), we finally reached the level when 5 million was already not enough. But the implementation in FPGA of various truncated configurations of the future microcircuit made it possible to test its operation. For example, they sold two cores (RISC + DSP) with a truncated set of peripherals or one core (RISC), but the entire periphery.

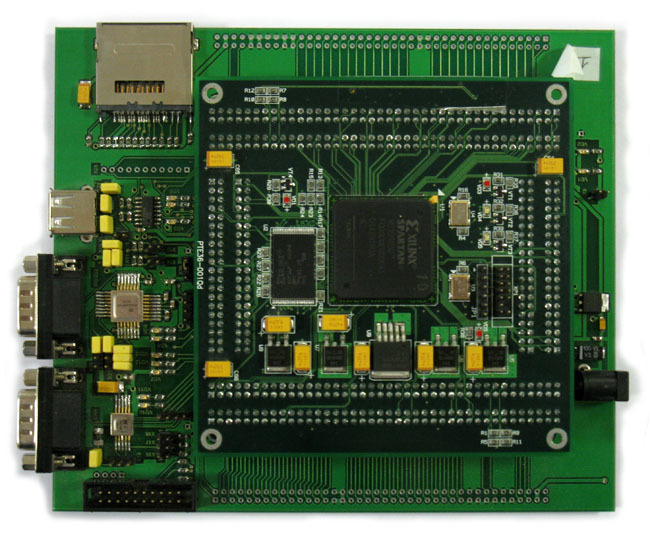

The new project required a new board, since the required amount of internal memory for the new 32-bit DSP core already exceeded the available capacity in the largest Spartan FPGA. I had to switch to more expensive and complex FPGAs. The project time was limited, and decided to find a ready-made solution. The choice fell on the board from INREVIUM with the largest at that time FPGA Xilinx Virtex-6 XC6VLX760.

And although the number of equivalent gates has increased to only 8 million, but the amount of built-in block memory has increased from 2 Mbit to 25 Mbit.

The choice also most likely determined that the cost of the fee was preserved on the site of the German representative office in Google’s cache, and we knew that it would cost $ 18K before signing any NDA. And with the cost of only one FPGA chip of $ 15 thousand, this removed any questions about developing your own board. Serial boards for such large FPGAs usually cost either as much as the FPGAs themselves or are slightly more expensive.

The acquisition of the board also brought a lot of interesting knowledge, for example, our local distributor was convinced that this board costs $ 40K including shipping, and in general it risks very much with 100% prepayment on our part. Ultimately, 3 of these boards were purchased without intermediaries and are now used to prototype our DSP processors.

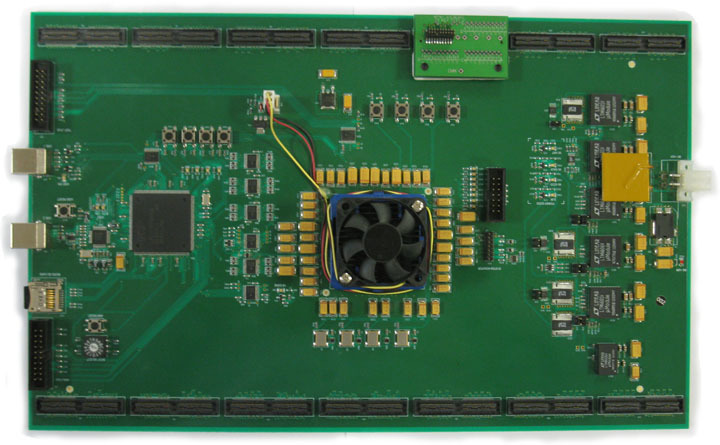

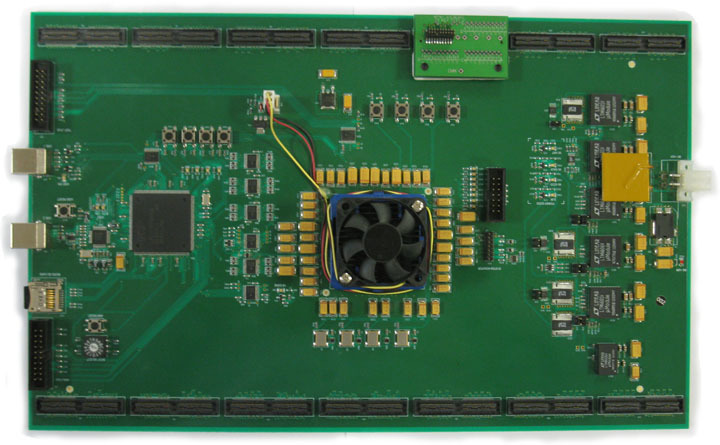

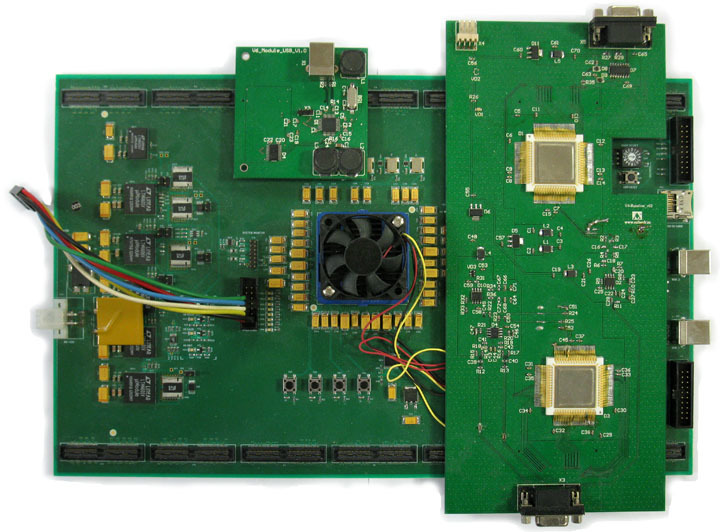

For the new 32-bit specialized microcontroller, it was decided to try to make your own board. Firstly, developers of modules on FPGAs should develop and not be afraid to use microcircuits that are more expensive than their personal cars, and secondly, one of the distributors had several Virtex-6 XC6VLX550T in stock and he offered them at a large discount. The FPGA LX550T is one step smaller than the LX760 (about 30% fewer valves), but the final price of the boards, taking into account the development, was only about $ 8K. 6 boards were assembled. We did not plan to distribute them to customers, but organized for developers access to them via the Internet. The board has implemented many interesting solutions. For example, firmware files were loaded onto the board as on a MassStorage Device into a special SD card, and then they were loaded from it into the FPGA. In total, the card can have up to 10 different firmwares, and through a special control program you can choose which one to use at the moment. Also implemented various protections "from the fool", so as not to accidentally burn an expensive chip. All this allows you to work with these boards remotely, safely and trust them even to students. The designed MK in FPGA worked at a frequency of 40 MHz.

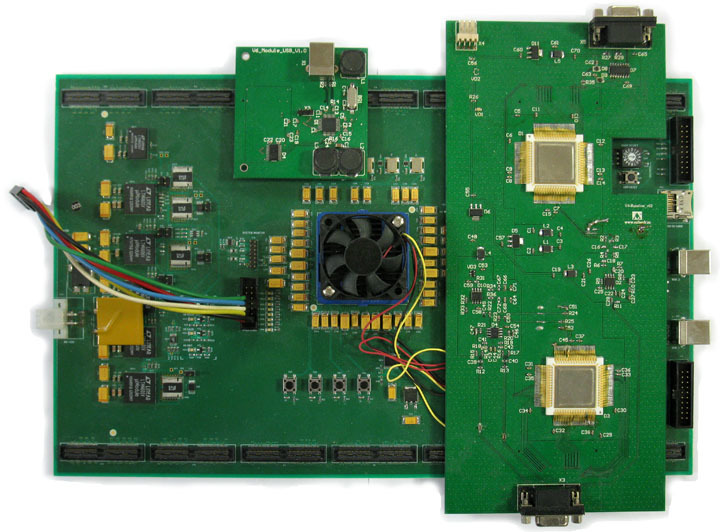

The board itself (prototype of a specialized dual-core 32-bit microcontroller):

Prototype of a specialized chip for angle-to-code conversion sensors:

Unfortunately, there are several drawbacks to this board: bad connectors are selected for connecting additional modules, but this is half the trouble, we forgot to fix holes near the connectors, and the modules are actually held only in the connectors. Also, to access some of the controls on the main board, you have to figure out the expansion modules.

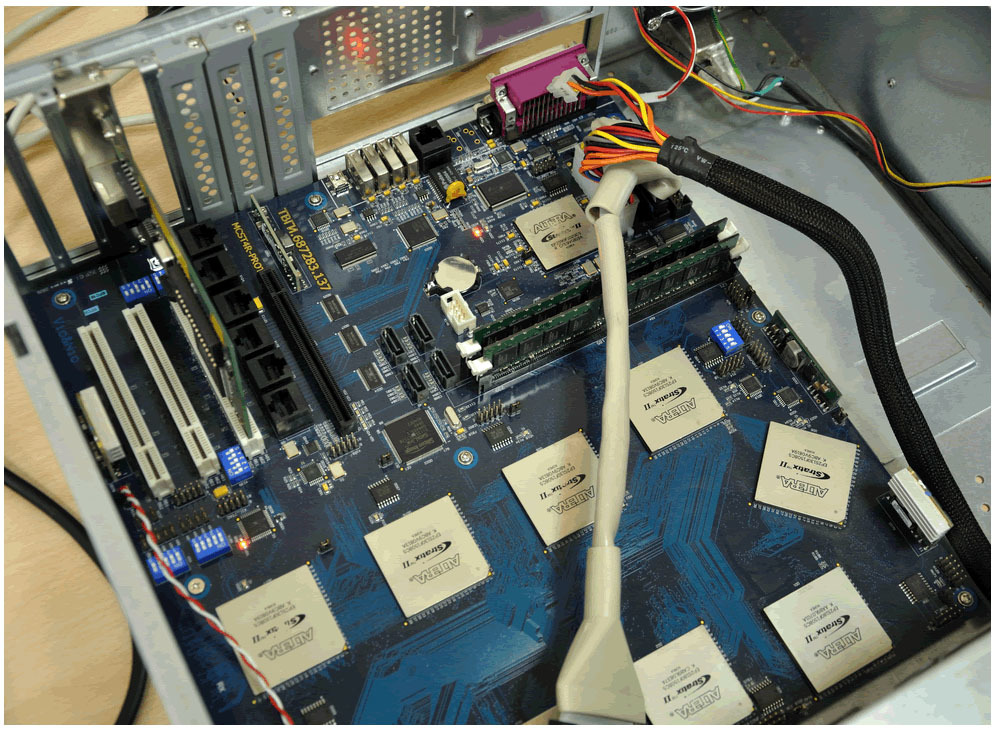

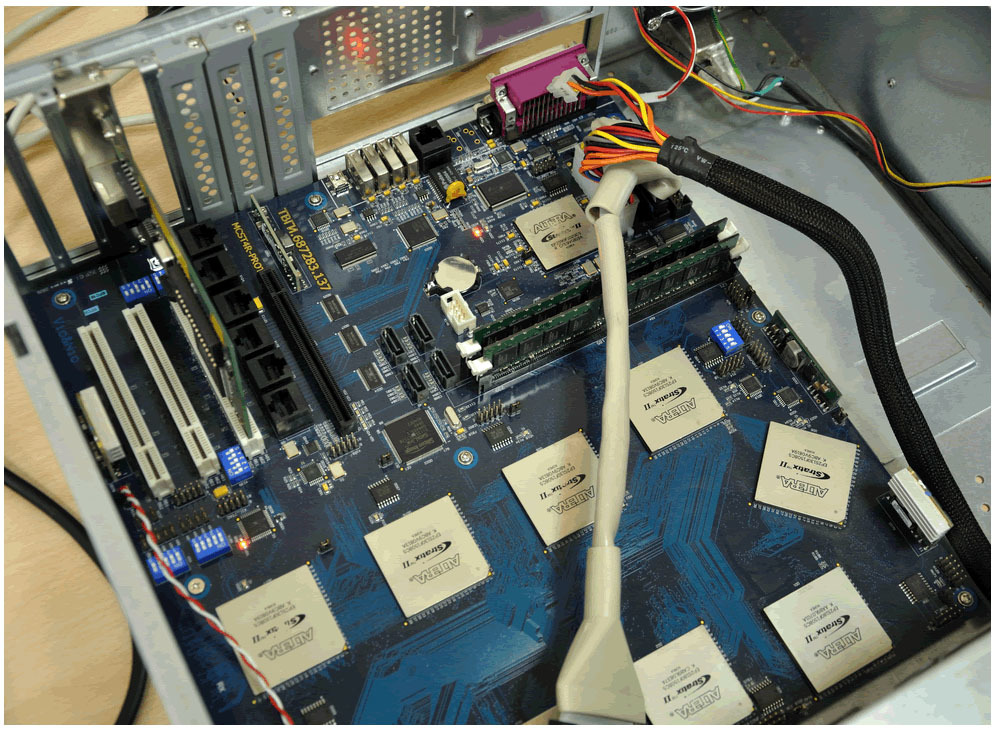

But what about other custom chip developers? For example, the MCST when prototyping the VLSI 1891ВМ6Я (R-1000, four-core processor with 64-bit SPARC v.9 architecture) used a specialized board with 10 Altera Stratix II FPGAs (4 x EP2S180 + 5 x EP2S130 + 1 x EP2S90). The total volume of logical gates of the system can be estimated at 20 million.

Now one EP2S180 chip costs about $ 8K. So the cost of only FPGA chips in the prototype exceeds $ 50K.

For prototyping the Elbrus-4C + processor, 21 Altera Stratix IV EP4SE820 microcircuits with a total volume of 100 million valves were required (although the MCST itself gives a figure of 750 million) and costs about $ 200K. At the same time, the working frequency of the prototype is 9 MHz.

Now specialized solutions for FPGA prototyping are offered by companies specializing in the development of CAD tools for microelectronics, although modules suitable for prototyping can also be found at other companies. Intel and IBM have FPGA prototypes, but their characteristics are not advertised, and they become known to a wide circle only when the prototype is already outdated.

Cadence offers a special Rapid Prototyping Platform built on the Altera Stratix-4 EP4SE820 FPGA. In the minimum configuration, the platform consists of two (with a total volume of 10 million gates), in a maximum of six FPGAs (with a volume of up to 30 million gates). The price of one EP4SE820 chip today is ~ $ 10K.

The new system from Cadence is called Protium and is based on the Xilinx Virtex-7 XC7V2000T and allows you to implement from 25 million in two FPGAs to 100 million valves in eight. The cost of one XC7V2000T chip is now about $ 20K. Those. fully equipped Protium will cost at least $ 160K.

Aldec, in addition to development tools, also offers a platform for FPGA prototyping HES-7.

Up to six Xilinx Virtex-7 XC7V2000T or UltraSacle XCVU440 are located on one board. In the case of the implementation of the module based on the FPGA UltraSacle XCVU440, the total number of valves reaches 158 million. Using an additional board, you can assemble 24 FPGA chips into a single module and get 633 million valves. The cost of one XCVU440 chip is now $ 49K. And the maximum total cost of all FPGAs exceeds $ 1M.

Synopsys has probably the most experience in developing platforms for FPGA prototyping. Their early models were based on the FPGA Virtex-6 (HAPS-60), then Virtex-7 (HAPS-70). Their latest development, HAPS-80, in a single module contains from one to four FPGAs Xilinx UltraScale XCVU440.

Ready-made modules can be combined into a single rack. And in this case, the total volume is a record 1.6 billion valves.

When using one FPGA, the maximum frequency is up to 300 MHz, when using neighboring ones in one module to 100 MHz, when using several modules, the frequency is reduced to 30 MHz.

Thus, having approximately $ 3.5M for the purchase of FPGAs, you can assemble a platform suitable for prototyping Intel Xeon E7. Well, or wait 20 years, when FPGAs of such a volume will fall in price to a couple of hundred dollars.

Prototyping future chips on an FPGA is the only way to test how the circuit works on real-world tasks in less real-time. The prototype allows you to debug software, get initial performance characteristics, and much more. Modern FPGAs have a sufficiently large amount of resources for these tasks. For example, you yourself can implement a full-fledged computer with an Intel 8086 processor on a motherboard with FPGA for $ 300 .

2004 year

Unfortunately, we could not find the very first prototype in the deposits of our cabinet with skeletons, but it was a small scarf based on the Xilinx Spartan3-400 (XC3S400). 400 means the number of thousands of valve equivalents that are available to the developer to create their circuit. The price of the handkerchief was approximately $ 50 and allowed to implement in it a simple 8-bit microcontroller with all memory and at a frequency of 40 MHz. Prototyping consisted in the fact that the developed microcontroller on it blinked an LED.

2005 year

The special board for the prototype was already developed not as an experiment, but as a meaningful stage of the project. Already applied FPGA Xilinx Spartan3-1000. Those. 1 million valves were already available to us, and the designed microcontroller worked at its maximum frequency of 48 MHz. And it was on this board that I caught the very 2 lost bytes per gigabyte. The price of the board was approximately $ 200.

2007 year

For the new 32-bit microcontroller, it was obvious that 1 million valves might not be enough. Therefore, a new motherboard based on Xilinx Spartan3-5000 was developed, thanks to which 5 million valves have already become available. The price of the board was approximately $ 500 and for a long time this board became the main one for prototyping new developments. On its basis, not only microcontrollers were tested, but also various specialized microcircuits. The designed microcontroller in FPGA was already operating at a reduced frequency of 20 MHz, although then in silicon it worked at frequencies of 100 MHz and even 150 MHz.

Prototype of a 32-bit microcontroller:

Prototype of a video card (unfortunately, the project did not go live, but the finished RTL is waiting in the wings):

Prototype of a 4-way Ethernet switch with built-in transceivers:

2010 year

When developing a dual-core microcontroller (32-bit RISC + 16-bit DSP core), we finally reached the level when 5 million was already not enough. But the implementation in FPGA of various truncated configurations of the future microcircuit made it possible to test its operation. For example, they sold two cores (RISC + DSP) with a truncated set of peripherals or one core (RISC), but the entire periphery.

year 2012

The new project required a new board, since the required amount of internal memory for the new 32-bit DSP core already exceeded the available capacity in the largest Spartan FPGA. I had to switch to more expensive and complex FPGAs. The project time was limited, and decided to find a ready-made solution. The choice fell on the board from INREVIUM with the largest at that time FPGA Xilinx Virtex-6 XC6VLX760.

And although the number of equivalent gates has increased to only 8 million, but the amount of built-in block memory has increased from 2 Mbit to 25 Mbit.

The choice also most likely determined that the cost of the fee was preserved on the site of the German representative office in Google’s cache, and we knew that it would cost $ 18K before signing any NDA. And with the cost of only one FPGA chip of $ 15 thousand, this removed any questions about developing your own board. Serial boards for such large FPGAs usually cost either as much as the FPGAs themselves or are slightly more expensive.

The acquisition of the board also brought a lot of interesting knowledge, for example, our local distributor was convinced that this board costs $ 40K including shipping, and in general it risks very much with 100% prepayment on our part. Ultimately, 3 of these boards were purchased without intermediaries and are now used to prototype our DSP processors.

year 2013

For the new 32-bit specialized microcontroller, it was decided to try to make your own board. Firstly, developers of modules on FPGAs should develop and not be afraid to use microcircuits that are more expensive than their personal cars, and secondly, one of the distributors had several Virtex-6 XC6VLX550T in stock and he offered them at a large discount. The FPGA LX550T is one step smaller than the LX760 (about 30% fewer valves), but the final price of the boards, taking into account the development, was only about $ 8K. 6 boards were assembled. We did not plan to distribute them to customers, but organized for developers access to them via the Internet. The board has implemented many interesting solutions. For example, firmware files were loaded onto the board as on a MassStorage Device into a special SD card, and then they were loaded from it into the FPGA. In total, the card can have up to 10 different firmwares, and through a special control program you can choose which one to use at the moment. Also implemented various protections "from the fool", so as not to accidentally burn an expensive chip. All this allows you to work with these boards remotely, safely and trust them even to students. The designed MK in FPGA worked at a frequency of 40 MHz.

The board itself (prototype of a specialized dual-core 32-bit microcontroller):

Prototype of a specialized chip for angle-to-code conversion sensors:

Unfortunately, there are several drawbacks to this board: bad connectors are selected for connecting additional modules, but this is half the trouble, we forgot to fix holes near the connectors, and the modules are actually held only in the connectors. Also, to access some of the controls on the main board, you have to figure out the expansion modules.

Domestic experience

But what about other custom chip developers? For example, the MCST when prototyping the VLSI 1891ВМ6Я (R-1000, four-core processor with 64-bit SPARC v.9 architecture) used a specialized board with 10 Altera Stratix II FPGAs (4 x EP2S180 + 5 x EP2S130 + 1 x EP2S90). The total volume of logical gates of the system can be estimated at 20 million.

Now one EP2S180 chip costs about $ 8K. So the cost of only FPGA chips in the prototype exceeds $ 50K.

For prototyping the Elbrus-4C + processor, 21 Altera Stratix IV EP4SE820 microcircuits with a total volume of 100 million valves were required (although the MCST itself gives a figure of 750 million) and costs about $ 200K. At the same time, the working frequency of the prototype is 9 MHz.

Foreign experience

Now specialized solutions for FPGA prototyping are offered by companies specializing in the development of CAD tools for microelectronics, although modules suitable for prototyping can also be found at other companies. Intel and IBM have FPGA prototypes, but their characteristics are not advertised, and they become known to a wide circle only when the prototype is already outdated.

Cadence offers a special Rapid Prototyping Platform built on the Altera Stratix-4 EP4SE820 FPGA. In the minimum configuration, the platform consists of two (with a total volume of 10 million gates), in a maximum of six FPGAs (with a volume of up to 30 million gates). The price of one EP4SE820 chip today is ~ $ 10K.

The new system from Cadence is called Protium and is based on the Xilinx Virtex-7 XC7V2000T and allows you to implement from 25 million in two FPGAs to 100 million valves in eight. The cost of one XC7V2000T chip is now about $ 20K. Those. fully equipped Protium will cost at least $ 160K.

Aldec, in addition to development tools, also offers a platform for FPGA prototyping HES-7.

Up to six Xilinx Virtex-7 XC7V2000T or UltraSacle XCVU440 are located on one board. In the case of the implementation of the module based on the FPGA UltraSacle XCVU440, the total number of valves reaches 158 million. Using an additional board, you can assemble 24 FPGA chips into a single module and get 633 million valves. The cost of one XCVU440 chip is now $ 49K. And the maximum total cost of all FPGAs exceeds $ 1M.

Synopsys has probably the most experience in developing platforms for FPGA prototyping. Their early models were based on the FPGA Virtex-6 (HAPS-60), then Virtex-7 (HAPS-70). Their latest development, HAPS-80, in a single module contains from one to four FPGAs Xilinx UltraScale XCVU440.

Ready-made modules can be combined into a single rack. And in this case, the total volume is a record 1.6 billion valves.

When using one FPGA, the maximum frequency is up to 300 MHz, when using neighboring ones in one module to 100 MHz, when using several modules, the frequency is reduced to 30 MHz.

Thus, having approximately $ 3.5M for the purchase of FPGAs, you can assemble a platform suitable for prototyping Intel Xeon E7. Well, or wait 20 years, when FPGAs of such a volume will fall in price to a couple of hundred dollars.

Only registered users can participate in the survey. Please come in.

In the meantime, can you guess how much the top-end FPGA Altera Stratix 10 GX / SX 5500 will cost?

- 16.3% less than 20K $ 23

- 21.2% from $ 20K to $ 40K 30

- 31.9% from $ 40K to $ 80K 45

- 30.4% over 80K $ 43