Programmable valve arrays: how will they help 5G networks

In early October, the company Xilinx introduced a new chip Versal, built on a programmable valve array ( FPGA ). The logic of such a device can be modified at any time during use. It is expected that the chip will accelerate the work of AI systems and will find application in 5G networks. The release of the processor is scheduled for the end of 2019.

Next, we talk about the device and how it will help the networks of the new generation.

/ Flickr / mike mozart / cc

5G technology uses high frequencies - 28 GHz and higher - so the signal is poorly transmitted over long distances. Plus the spread of its strongly interfere with the walls of houses. In a city, this can lead to a decrease in the quality of the connection.

Experts say that this will become an obstacle to the work of a large number of IoT devices, the active growth of which is predicted from 2020 (just when full 5G networks will be deployed).

Connected devices, such as cars or wearable medical gadgets, must exchange real-time data. The instability of the connection may prevent them from adequately assessing the situation around them or transferring vital data (for example, about the state of human health) to the servers of the service organization. Companies plan to solve this problem by arranging special distributed antenna systems, however, difficulties arise with this.

For example, now in New York there are over a thousand base stations. To cover the entire city with a 5G network, you will need to install another half a million . The cost of the project will be much higher than in the case of the previous "G-standards".

The Xilinx device will help solve problems with the stability of the Internet connection using AI systems, to work with which it is “sharpened”. Versal chip will be engaged in the processing of machine learning algorithms to 5G networks, optimizing directivity pattern of mobile communication antennas. This will allow to avoid blind sectors and choose the appropriate mode of data transmission.

Also, AI systems will improve handover algorithms that are responsible for transferring sessions from one station to another. Networks will also self-repair and adapt, automatically redirecting data if a node fails. So, 5G users will be able to freely move around the building or the city without failing to connect.

Xilinx already has customers for 5G AI-chips. Versal processors will be used for networking at the Olympics 2020.

The concept of Versal company Xilinx introduced in October. The new microcircuit is heterogeneous , that is, it uses several computational blocks at once. These units can be processors, co-processors, integrated circuits ASIC and FPGA.

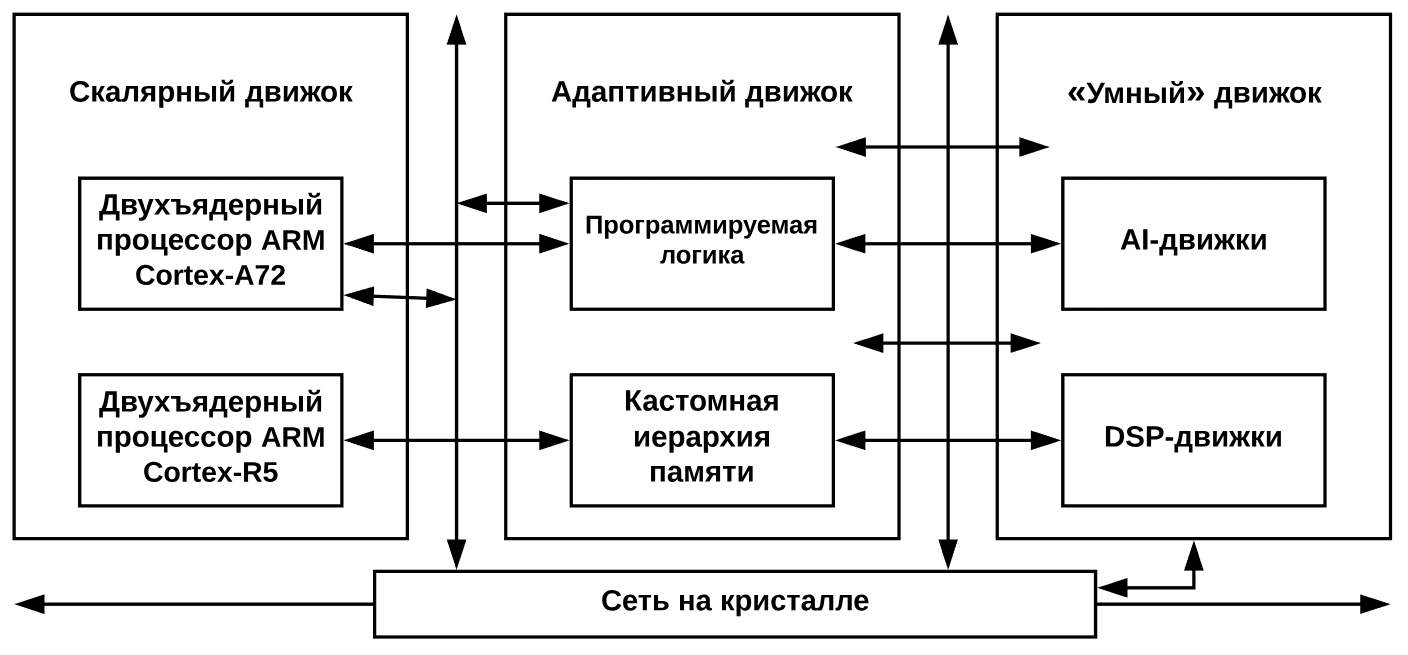

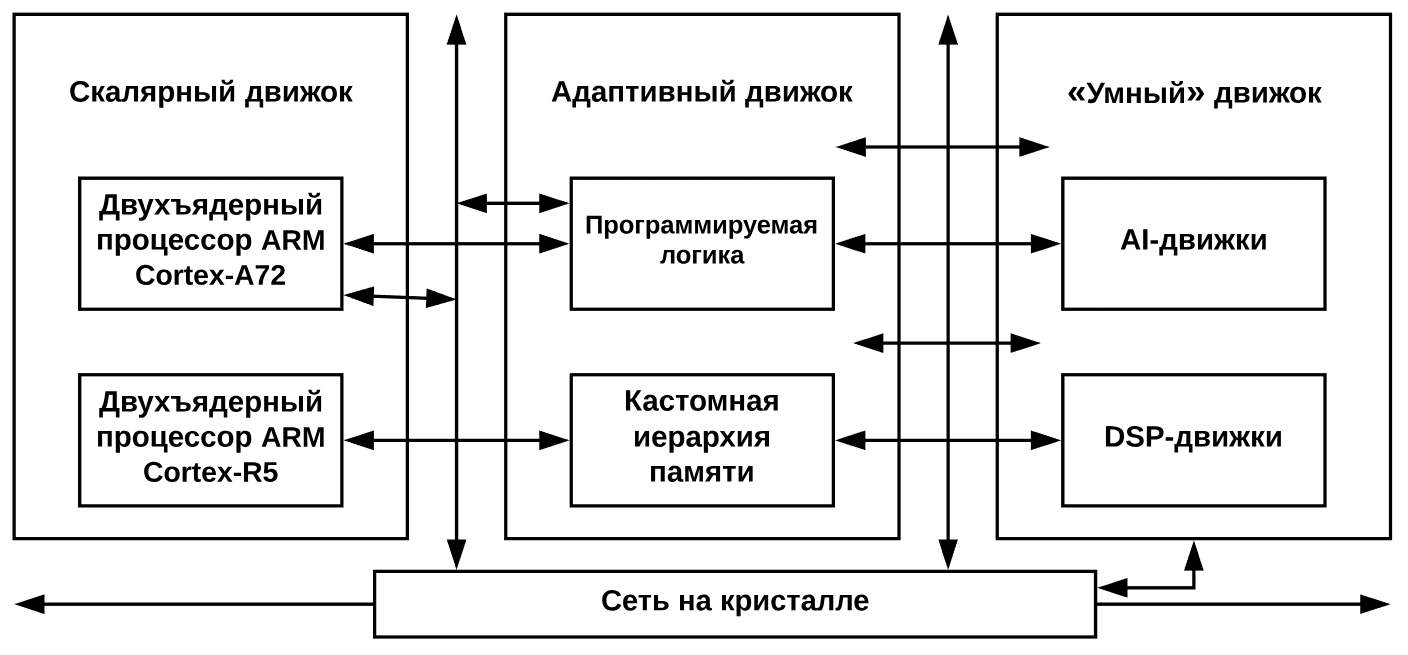

The new Xilinx chip is based on an improved version of the FPGA - Adaptive Computer Accelerator Platform (ACAP) architecture. It consists of four basic components: a scalar engine, an adaptive engine, vector accelerators (a “smart” engine), and a network on a chip (NoC - Network-on-Chip) for connecting system elements.

The scalar engine is represented by dual-core processors ARM Cortex-A72 and Cortex-R5. Programmable logic is based on configurable logic elements withlookup tables , triggers , memory and special blocks for connecting components. All this allows you to build a hierarchy of memory , sharpened for a specific computational problem.

The “smart” engine is based on the VLIW architecture , which is needed for parallel execution of several operations in a single instruction. The SIMD calculation principle is also applied . Such a structure helps to solve MO problems and process signals 5–10 times faster than classical systems. As for NoC, its declared throughput is 1 Tbit / s.

The ACAP architecture scheme looks like this.

Versal chips will be produced at TSMC at 7-nmtechnical process. Other features of the architecture can be found in the official PDF documents — the ASAP architecture overview and the Versal chip overview .

The system is programmed in C, C ++ and Python. According to the developers, they chose these PLs, since according to TIOBE , C, C ++ and Python are the most popular after Java.

In addition, these languages complement each other. C and C ++ are compiled, which means that the code can be run on bare metal (in particular, on FPGA). Python is better suited for data analysis and work with AI systems. Other arguments in favor of their choice of Xilinx lead in a separate study on the topic ( PDF ).

FPGA-based chips are being developed by other companies, such as Intel. From the latest products of the company can be distinguished hybrid device Arria . The development is a platform of two chips: Xeon E5-2600 v4 and Altera Arria 10 .

According to representatives of Intel, the device is suitable for servers, data centers and cloud services, where the load often increases abruptly. The processor on the FPGA will help to process data in parallel, which will increase the overall system performance. Fujitsu, for example, plans to supply this chip with its Primergy server line by the end of the year.

Other market players - AMD, ARM, Qualcomm, Samsung and others - in 2012 created a non-profit organization HSA Foundation. They promote heterogeneous computing: they develop industry standards, help developers enter the market and sponsor educational programs.

Xilinx believes that with the development of AI systems and the spread of 5G networks, the demand for FPGA platforms will increase. Xilinx CEO Victor Peng (Victor Peng) notes that the only obstacle to the mass production of chips - competition from the CPU and GPU, which does not allow FPGA-solutions to "capture" the market. But, probably, a surge in demand (if it does happen) should not be expected before 2020 .

PS Additional materials from the corporate blog VAS Experts:

PPS A couple of fresh articles from our blog on Habré:

Next, we talk about the device and how it will help the networks of the new generation.

/ Flickr / mike mozart / cc

5G network problem

5G technology uses high frequencies - 28 GHz and higher - so the signal is poorly transmitted over long distances. Plus the spread of its strongly interfere with the walls of houses. In a city, this can lead to a decrease in the quality of the connection.

Experts say that this will become an obstacle to the work of a large number of IoT devices, the active growth of which is predicted from 2020 (just when full 5G networks will be deployed).

Connected devices, such as cars or wearable medical gadgets, must exchange real-time data. The instability of the connection may prevent them from adequately assessing the situation around them or transferring vital data (for example, about the state of human health) to the servers of the service organization. Companies plan to solve this problem by arranging special distributed antenna systems, however, difficulties arise with this.

For example, now in New York there are over a thousand base stations. To cover the entire city with a 5G network, you will need to install another half a million . The cost of the project will be much higher than in the case of the previous "G-standards".

How to solve these problems Versal

The Xilinx device will help solve problems with the stability of the Internet connection using AI systems, to work with which it is “sharpened”. Versal chip will be engaged in the processing of machine learning algorithms to 5G networks, optimizing directivity pattern of mobile communication antennas. This will allow to avoid blind sectors and choose the appropriate mode of data transmission.

Also, AI systems will improve handover algorithms that are responsible for transferring sessions from one station to another. Networks will also self-repair and adapt, automatically redirecting data if a node fails. So, 5G users will be able to freely move around the building or the city without failing to connect.

Xilinx already has customers for 5G AI-chips. Versal processors will be used for networking at the Olympics 2020.

Chip architecture features

The concept of Versal company Xilinx introduced in October. The new microcircuit is heterogeneous , that is, it uses several computational blocks at once. These units can be processors, co-processors, integrated circuits ASIC and FPGA.

The new Xilinx chip is based on an improved version of the FPGA - Adaptive Computer Accelerator Platform (ACAP) architecture. It consists of four basic components: a scalar engine, an adaptive engine, vector accelerators (a “smart” engine), and a network on a chip (NoC - Network-on-Chip) for connecting system elements.

The scalar engine is represented by dual-core processors ARM Cortex-A72 and Cortex-R5. Programmable logic is based on configurable logic elements withlookup tables , triggers , memory and special blocks for connecting components. All this allows you to build a hierarchy of memory , sharpened for a specific computational problem.

The “smart” engine is based on the VLIW architecture , which is needed for parallel execution of several operations in a single instruction. The SIMD calculation principle is also applied . Such a structure helps to solve MO problems and process signals 5–10 times faster than classical systems. As for NoC, its declared throughput is 1 Tbit / s.

The ACAP architecture scheme looks like this.

Versal chips will be produced at TSMC at 7-nmtechnical process. Other features of the architecture can be found in the official PDF documents — the ASAP architecture overview and the Versal chip overview .

The system is programmed in C, C ++ and Python. According to the developers, they chose these PLs, since according to TIOBE , C, C ++ and Python are the most popular after Java.

In addition, these languages complement each other. C and C ++ are compiled, which means that the code can be run on bare metal (in particular, on FPGA). Python is better suited for data analysis and work with AI systems. Other arguments in favor of their choice of Xilinx lead in a separate study on the topic ( PDF ).

Similar solutions

FPGA-based chips are being developed by other companies, such as Intel. From the latest products of the company can be distinguished hybrid device Arria . The development is a platform of two chips: Xeon E5-2600 v4 and Altera Arria 10 .

According to representatives of Intel, the device is suitable for servers, data centers and cloud services, where the load often increases abruptly. The processor on the FPGA will help to process data in parallel, which will increase the overall system performance. Fujitsu, for example, plans to supply this chip with its Primergy server line by the end of the year.

Other market players - AMD, ARM, Qualcomm, Samsung and others - in 2012 created a non-profit organization HSA Foundation. They promote heterogeneous computing: they develop industry standards, help developers enter the market and sponsor educational programs.

Xilinx believes that with the development of AI systems and the spread of 5G networks, the demand for FPGA platforms will increase. Xilinx CEO Victor Peng (Victor Peng) notes that the only obstacle to the mass production of chips - competition from the CPU and GPU, which does not allow FPGA-solutions to "capture" the market. But, probably, a surge in demand (if it does happen) should not be expected before 2020 .

PS Additional materials from the corporate blog VAS Experts:

- DDOS and 5G: thicker "pipe" - more problems

- Internet to the village - we are building a radio-relay Wi-Fi network

PPS A couple of fresh articles from our blog on Habré: